Introduction

In this article, we’ll be using the Vivado Design Suite 2022.1 alongside the Vitis 2022.1 to create a basic “Hello World” project for the Mimas A7 Mini FPGA Development Board. The design will contain a MicroBlaze (32-bit) soft processor and peripherals connected together by AXI bus. More information and resources including a datasheet for MicroBlaze can be found at Xilinx’s MicroBlaze page. Advanced knowledge of MicroBlaze or AXI is not a prerequisite to follow this article.

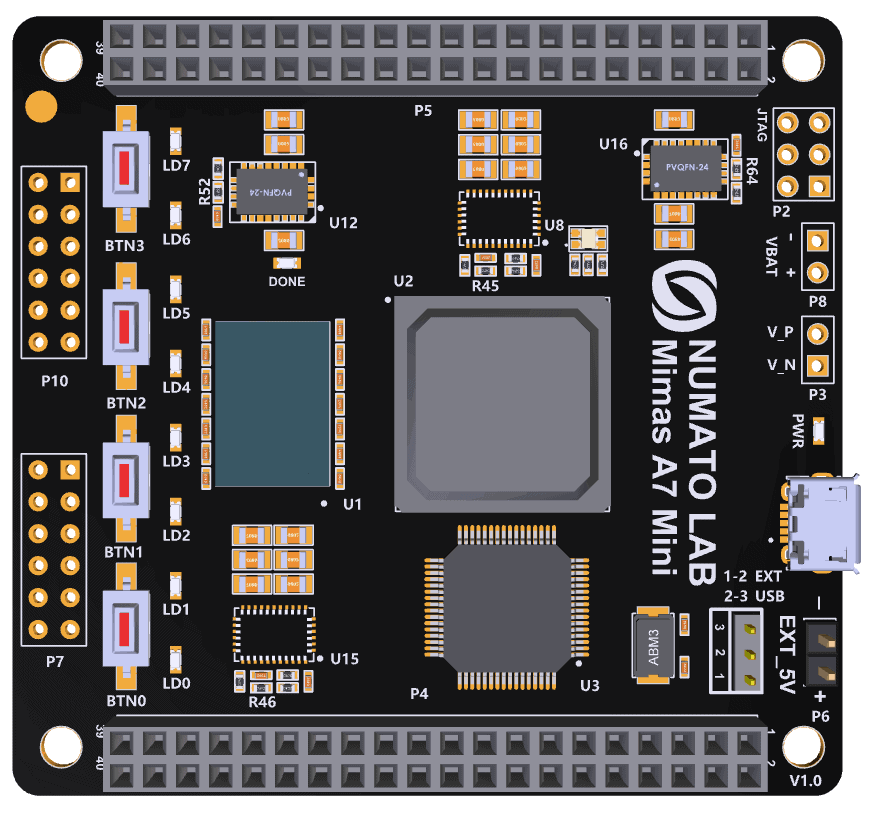

Mimas A7 Mini FPGA Development Board

The Mimas A7 Mini is an Artix-7 based replacement and upgrade of Numato Lab’s Mimas Spartan 6 FPGA Board. Mimas A7 Mini offers a USB interface that can be used to program the board as well as to do debugging or data transfer with the host. With an XC7A35T FPGA onboard, the Mimas A7 Mini FPGA Development Board is a great choice for learning, product development, and OEM integration.

Prerequisites:

Hardware:

- Mimas A7 Mini FPGA Development Board

- (Optional) Xilinx Platform Cable USB II JTAG debugger.

- USB A to Micro USB cable

Software:

- Vivado Design Suite with Vitis installed

Creating MicroBlaze based Hardware Platform for Mimas A7 Mini

The following steps will walk you through the process of creating a new project with Vivado and building a hardware platform with MicroBlaze soft processor using an IP integrator. Numato Lab’s Mimas Artix 7 Mini FPGA Development Board is used in this example but any compatible FPGA platform can be used with minor changes to the steps. Screenshots are added wherever possible to make the process easier for the reader.

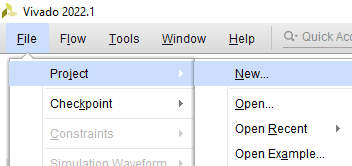

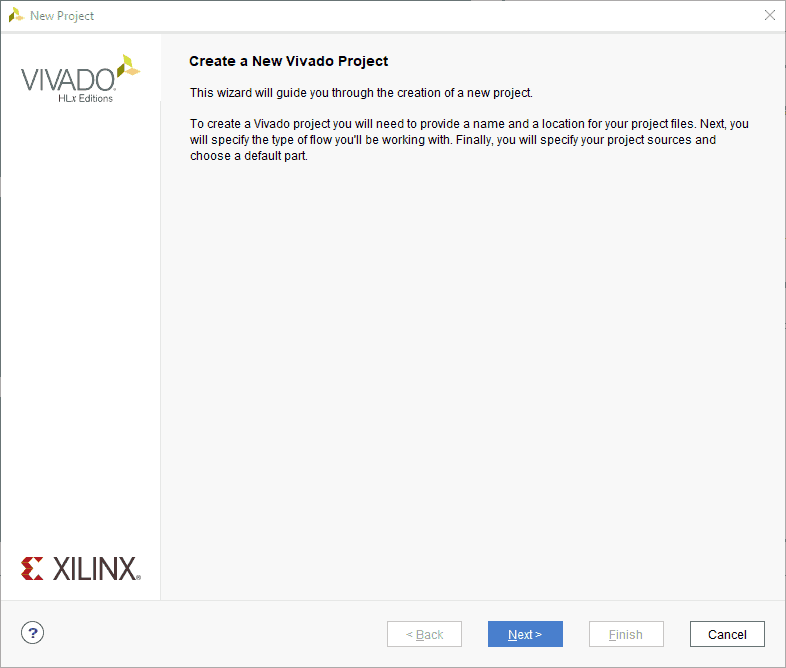

Step 1:

Launch Vivado Design Suite, go to “File->Project->New” to create a new project. The “New project” wizard will pop up. Click “Next” to continue.

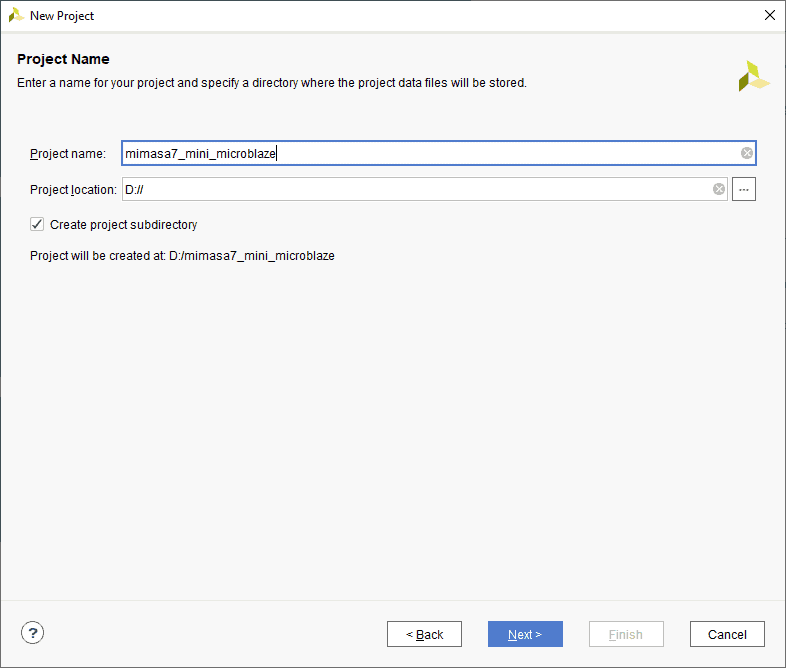

Step 2:

In the “Project Name” wizard, type in a name for the project and save it at a convenient location. For this example, we shall use “mimasa7_mini_microblaze” as the project name (feel free to use any name). Select the checkbox below to keep all project files in a single folder. Click “Next” to proceed.

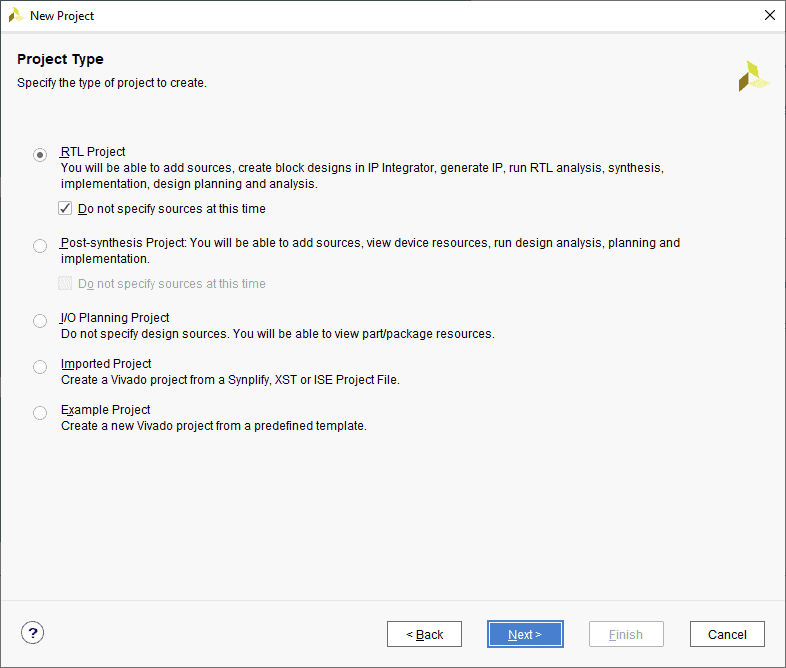

Step 3:

In the “Project type” wizard, select “RTL Project” and select the checkbox to skip specifying the source at the moment. Click “Next“.

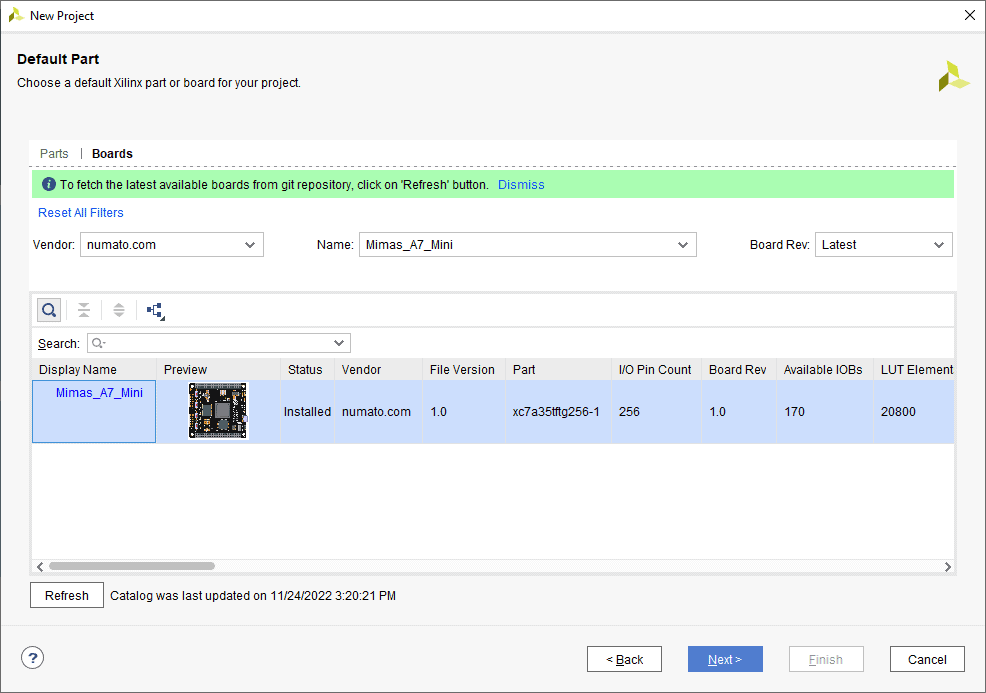

Step 4:

At the “Default Part” wizard, select “Boards” and then select “Mimas_A7_Mini” board. Click “Next” to continue. If Mimas_A7_Mini is not displayed in the Boards list, you need to install Mimas_A7_Mini board support files appropriately and retry this step. You can download Mimas A7 Mini board support files for Vivado here. Follow the readme in the link on how to install the Vivado board files in your system.

In the next wizard, click “Finish” to create a new project. When the new project wizard exits, a new project will open up in Vivado with the selected settings.

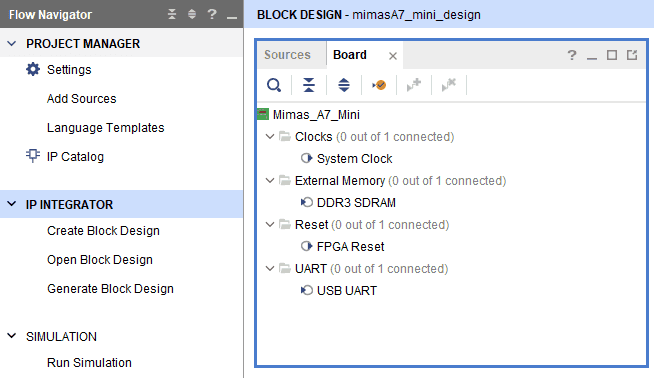

Step 5:

In the “Flow Navigator” panel, select “Create Block Design” under the IP integrator section. Give an appropriate name (Eg: “mimasa7_mini_design“) to the design and click “OK“. Select “Board” in the “Block Design” block. The default peripherals available for Mimas A7 Mini Board will be displayed.

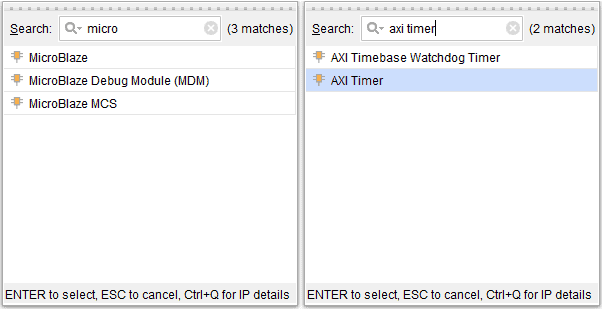

Step 6:

Add “System Clock“, “DDR3 SDRAM” and “USB UART” to the design by double-clicking the corresponding peripherals. In the “Diagram” window, right-click and select “Add IP” from the popup menu. Search for “MicroBlaze” & “AXI Timer” and add them to the design by double-clicking them.

Step 7:

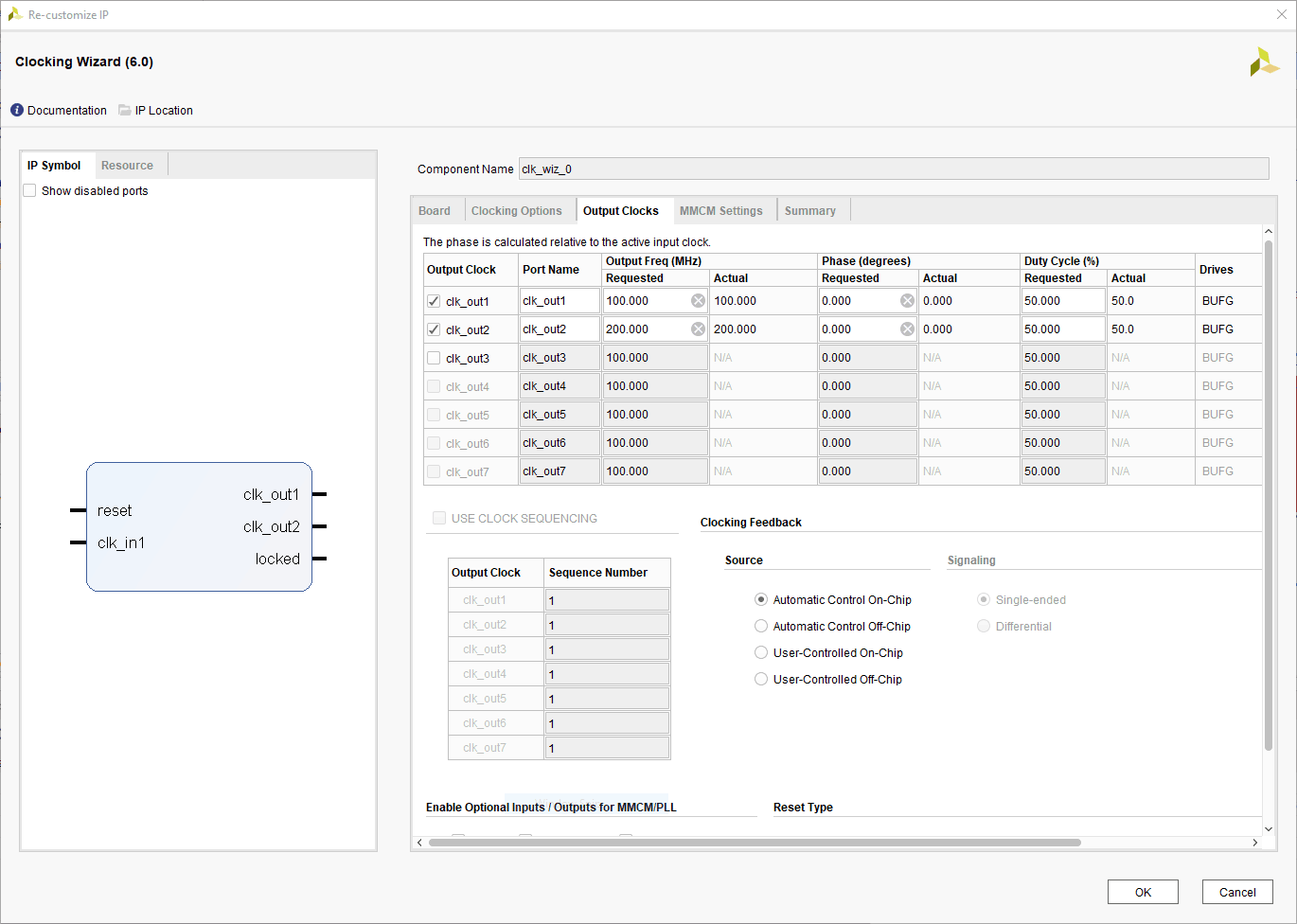

Double click “Clocking Wizard” IP and customize “Output Clocks” settings as shown in the following image.

Step 8

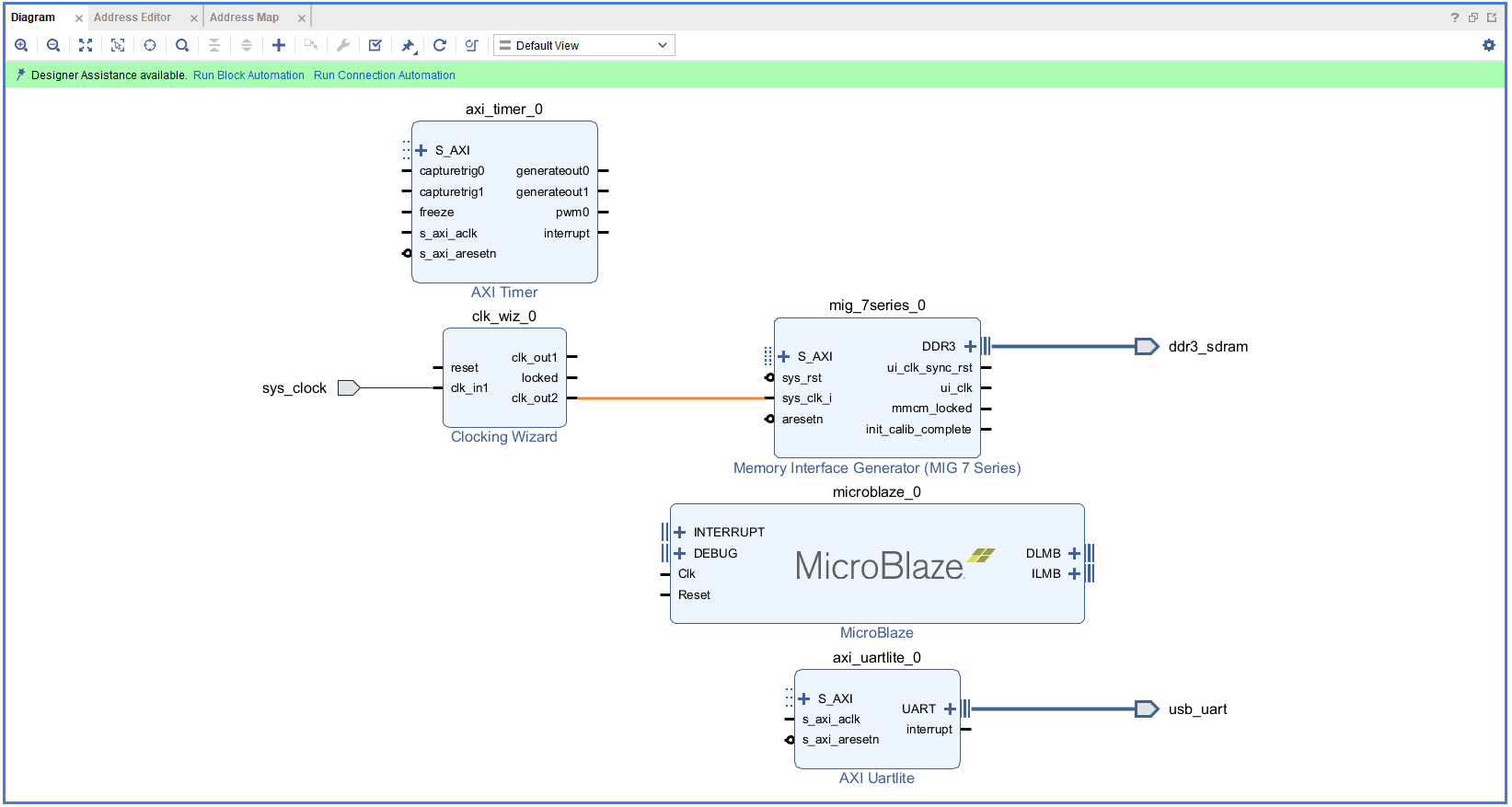

Remove existing “sys_clk_i” connection and input port (if any) and connect “clk_out2” net on the clocking Wizard to “sys_clk_i” of “MIG 7 Series” block as shown in the following image.

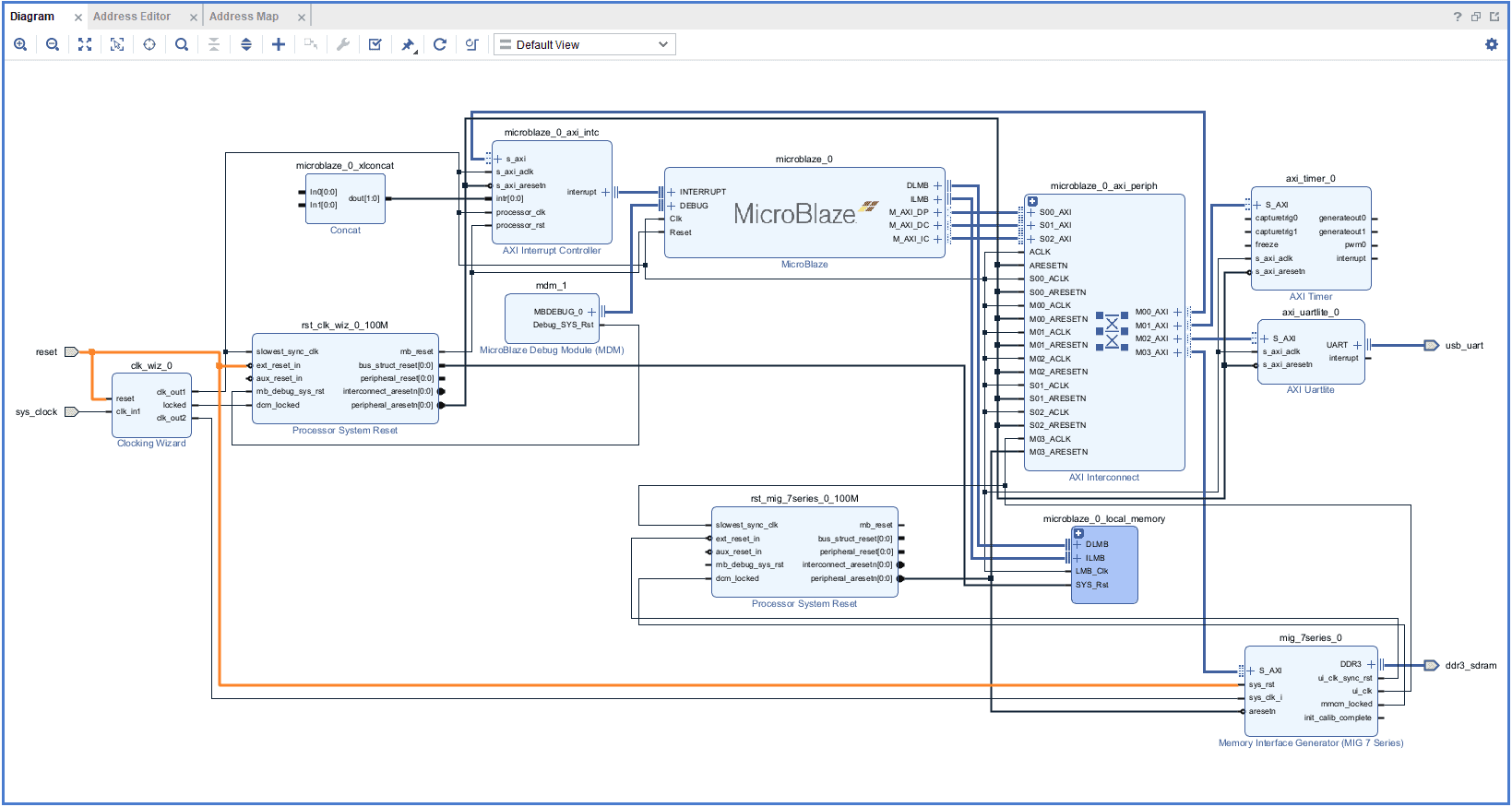

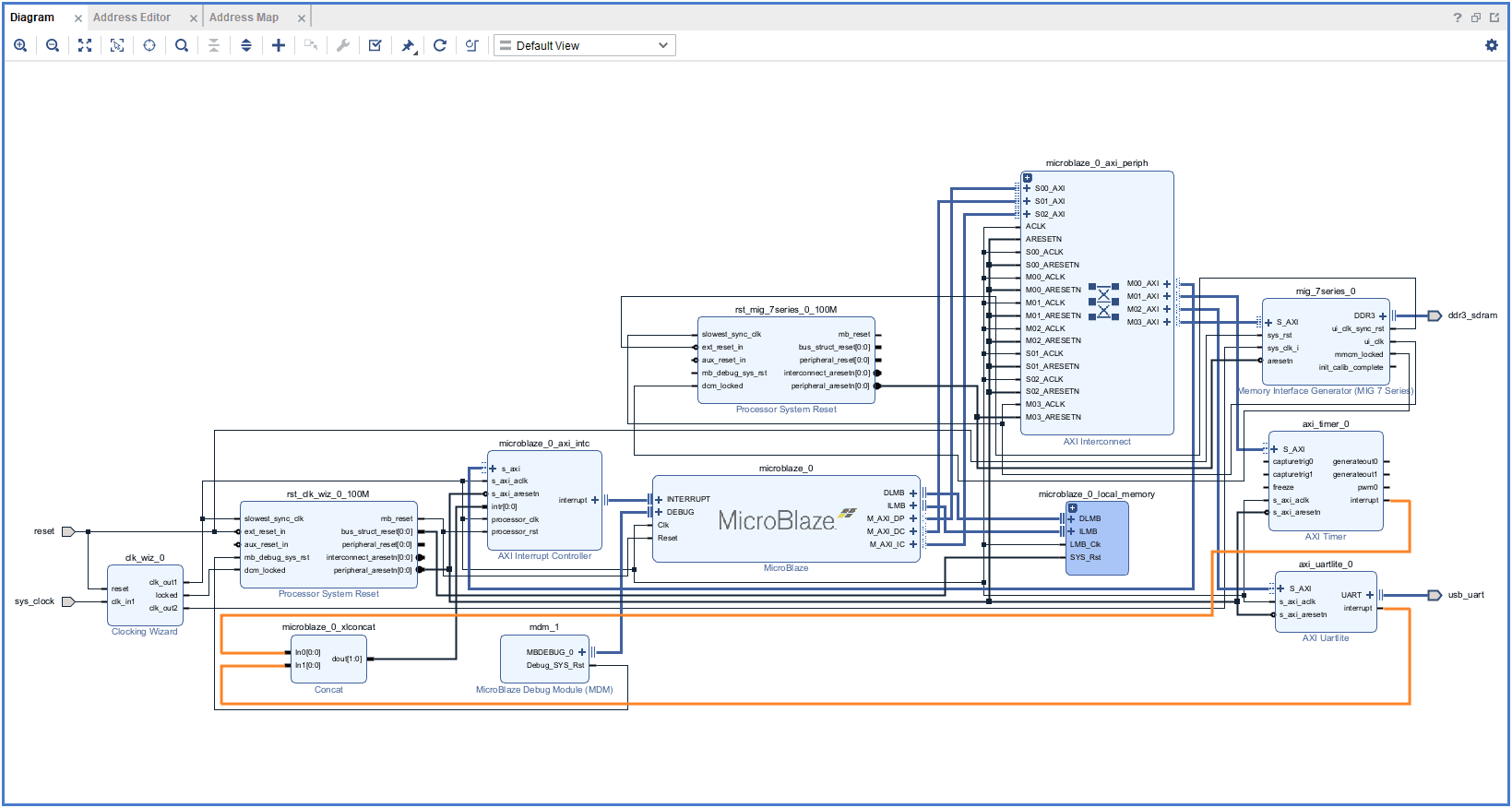

Step 9:

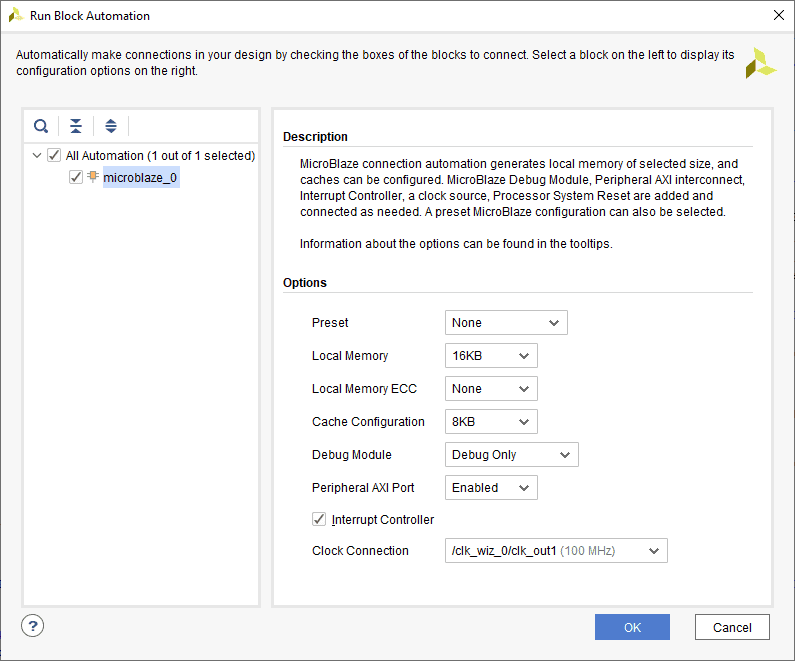

Click “Run Block Automation” present in the “Designer Assistance available” bar on the top left corner of the window to complete the design. Select the settings as shown in the following image. Click “OK” for Vivado to automatically configure the blocks for you. Once Block Automation is complete, run “Connection Automation” so Vivado can connect the blocks together to make a complete system.

Step 10:

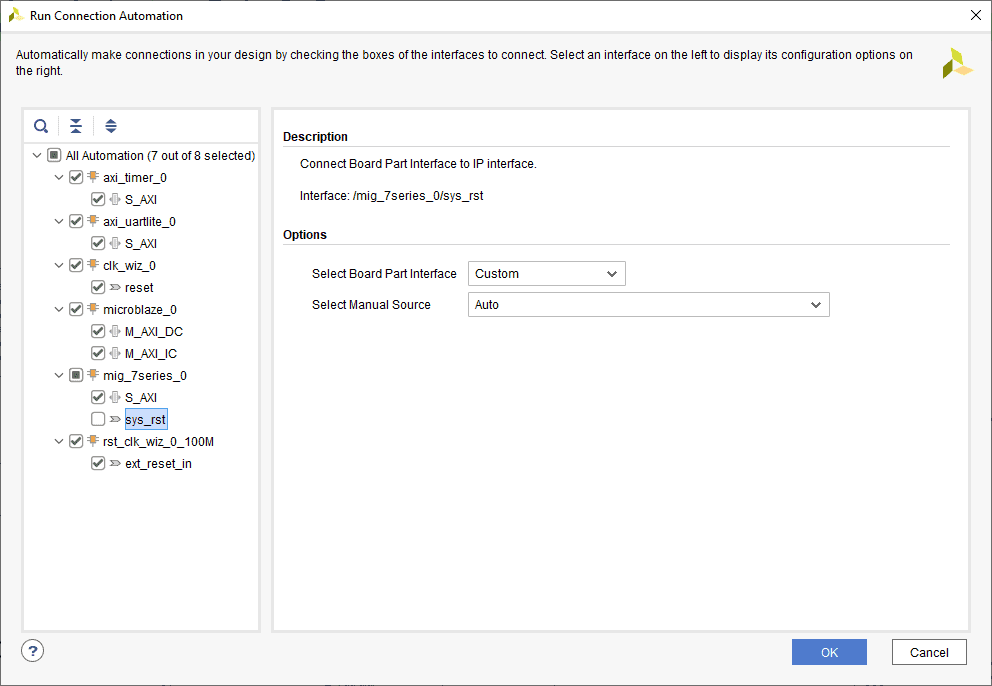

Run “Connection Automation” and select all the pins except “sys_rst” in “mig_7series_0“.

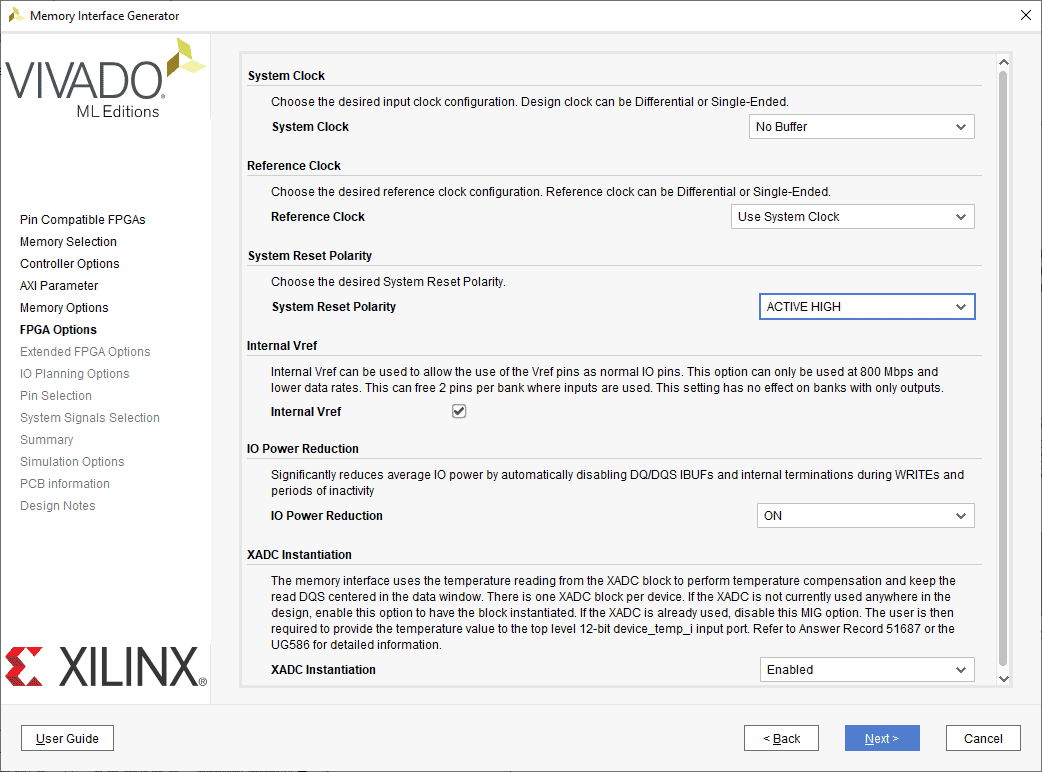

Step 11:

Double click on “mig_7series_0” to Re-customizing IP. Click “next” until we reach “FPGA Options“, change the “System Reset Polarity” to “Active High“and generate the IP.

Step 12:

Connect the “sys_rst” pin of “mig_7series_0” to the “reset” pin of “clk_wiz_0“.

Step 13:

Connect interrupt output lines from “AXI Timer” and “UARTLite” to the “Concat” block as shown in below figure. Select “Validate Design” option from the “Tools” menu to make sure that connections are correct.

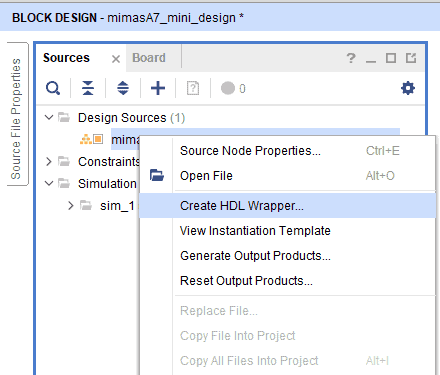

Step 14:

Right-click “mimasA7_mini_design” in the “Sources” window, select “Create HDL Wrapper” from the popup menu. Click “OK” on the window that appears to finish generating a wrapper.

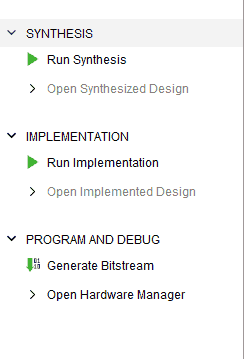

Step 15:

Click “Generate Bitstream” under the “Program And Debug” section to synthesize, implement and generate a bitstream.

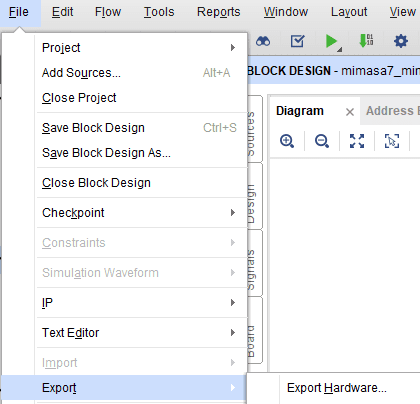

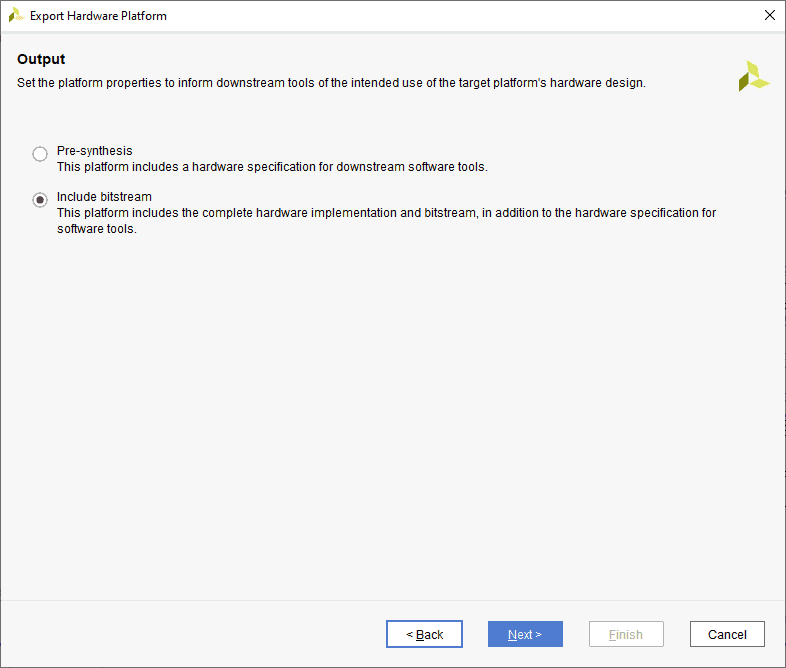

Step 16:

Once the implementation and generation of the bitstream are successfully completed, we need to export the hardware along with bitstream. Go to the “File” menu, select “Export->Export Hardware“. Select the “Include bitstream” checkbox and click “OK” in the “Export Hardware” wizard.

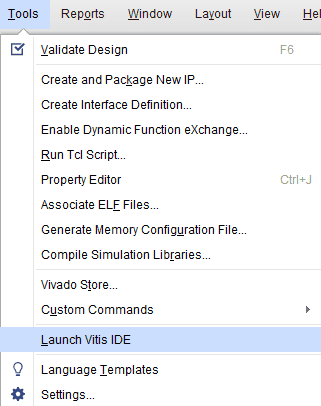

Step 17:

Select “Launch Vitis IDE” from the “Tools“. Provide a “Workspace” directory and click “Launch“.

Step 18:

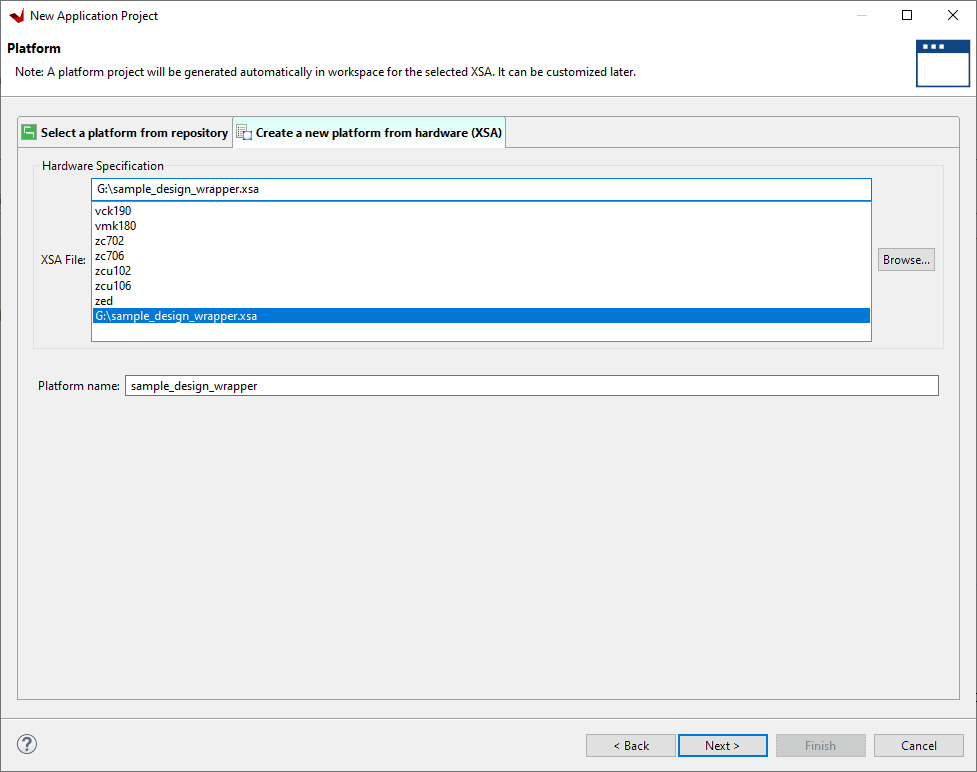

In the Vitis window, select “Create Application Project” and click “Next” in the dialog box that appears.

In the “Platform” window, select “Create a new platform from hardware” tab and import the “XSA file” which is already created (Provide XSA file location). Click “Next“.

Step 19:

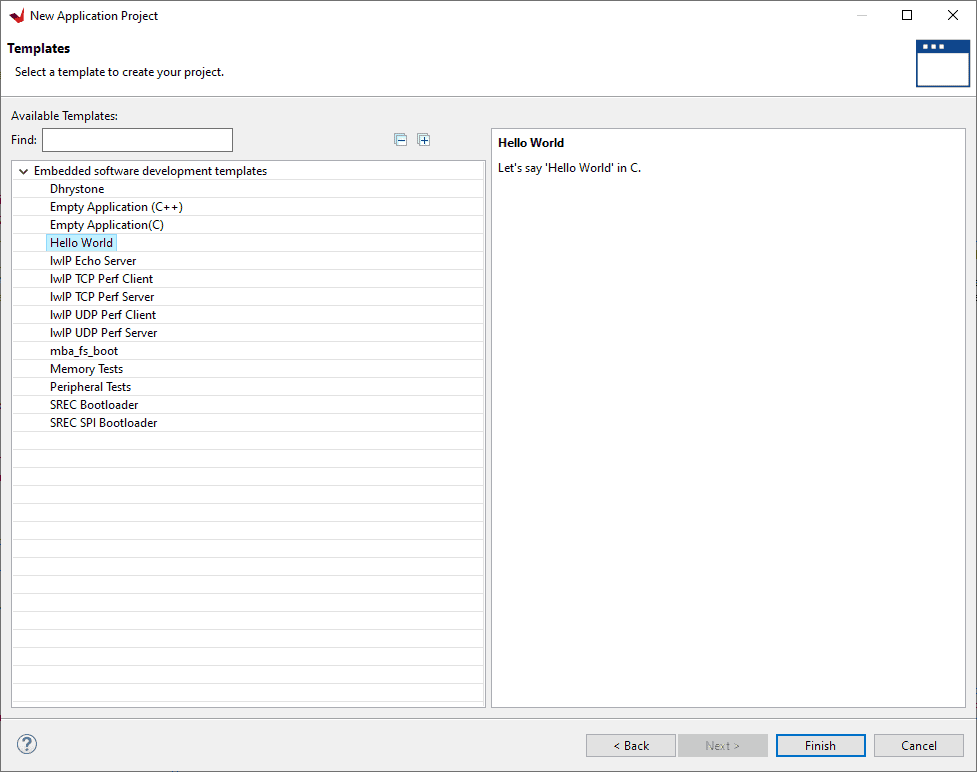

In the “Application Project Details” window, give an appropriate name for the Vitis Project and click “Next“. Click “Next” in the “Domain” window. Select the “Hello World” template from the list of available templates and click “Finish“.

Step 20:

Build the project. Once the build is completed successfully, power up Mimas A7 Mini using an external DC power supply and connect the Xilinx Platform USB cable to the board.

Step 21:

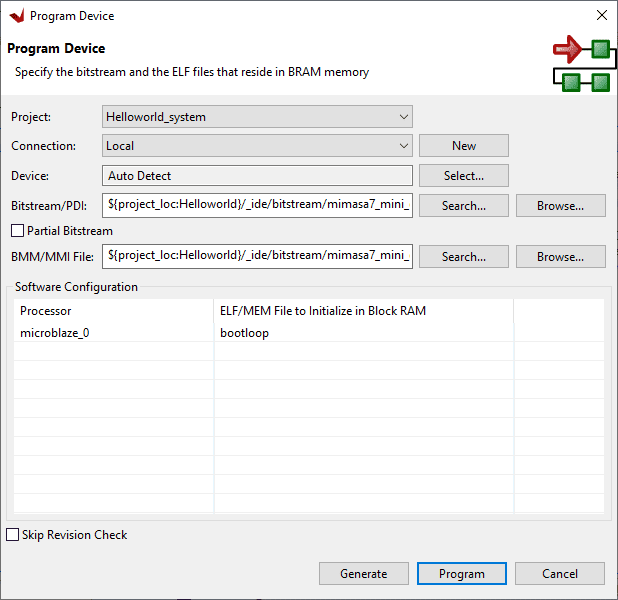

Program the FPGA on Mimas A7 Mini with a simple boot loop program by selecting the “Program FPGA” option from the “Xilinx” menu

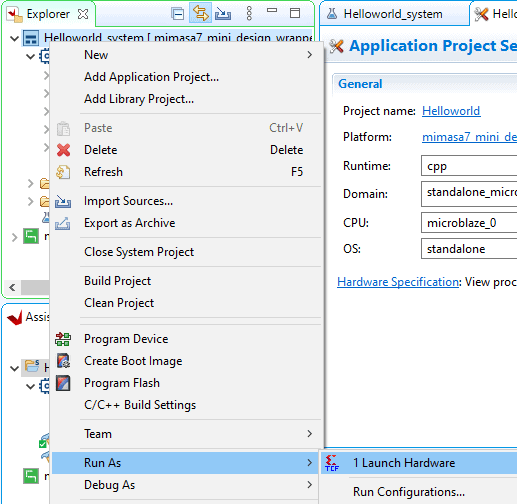

Step 22:

Open the COM port corresponding to Mimas A7 Mini in any serial terminal (PuTTY, Tera Term, etc.) with a 9600 baud rate (the default baud rate given in UART IP). Now, right-click on the “.elf file” in Project Explorer and select “Launch Hardware” as shown below.

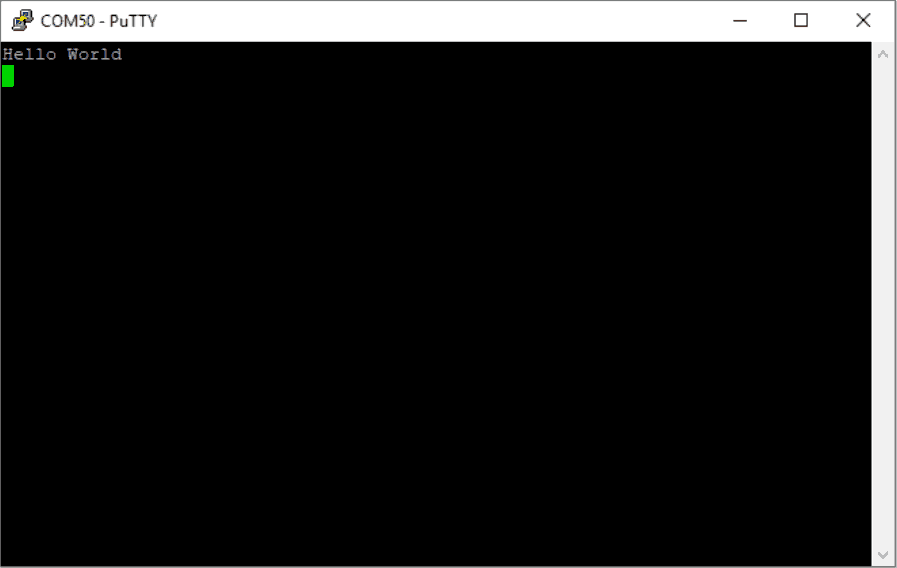

If everything went well, the application running on the board should print “Hello World” over the USB UART and should be displayed on the Serial Terminal application.