Introduction

Vivado Design Suite is developed by Xilinx and is used for the synthesis and analysis of HDL design with additional features for SOC development and high-level synthesis. Xilinx recommends the use of Vivado Design Suite for new designs with Ultra scale, Virtex-7, Kintex-7, Artix-7, and Zynq-7000. Complete pack of Vivado Design Suite contains Vivado High-Level Synthesis, Vivado Simulator, Vivado IP Integrator and Vivado TCL Store. In this article, we will be using Vivado IP Integrator along with Vivado SDK to create a basic “Hello World” project for HSFPX002 FPGA Module. The design will contain a MicroBlaze soft processor and peripherals connected by the AXI bus. Thanks to the excellent tools provided by Xilinx, most of the design can be done without writing any code at all.

What is MicroBlaze?

MicroBlaze is a 32-bit soft processor IP developed by Xilinx for their mid – high-end FPGA devices. MicroBlaze is compatible with Xilinx’s 6 and 7 series devices before mentioned as Spartan 6, Artix-7, Kintex-7, Virtex-7 and Zynq-7000 devices. More information and resources including a datasheet for MicroBlaze can be found on Xilinx’s MicroBlaze page. MicroBlaze IP is bundled with the Xilinx IP integrator. MicroBlaze based embedded design can use either PLB or AXI as the bus system. Since Xilinx is planning to phase out PLB and keep only AXI in the future, we will stick with AXI for our designs. Advanced knowledge of MicroBlaze or AXI is not a prerequisite to follow this article and build a working system successfully.

What is AXI?

AXI stands for Advanced eXtensible Interface. AXI is a bus interconnect based on ARM’s popular AMBA bus architecture. In a MicroBlaze system, AXI connects the microprocessor to all peripherals in the system. The only exception is Block RAM which is attached to the processor through LMB (Local Memory Bus). AXILite is available for connecting low throughput peripherals to the system such as UART, GPIO, etc.… AXILite uses fewer logic resources on FPGA compared to AXI. Usually, AXI is used to connect high throughput peripherals such as DDR memory, Ethernet, etc… Again, a detailed understanding of AXI is not required for following this article. But for curious readers, AXI Reference Guide is available here.

HSFPX002 FPGA Development Board

HSFPX002 is an easy to use FPGA Module featuring the Xilinx Artix 7 FPGA with 2Gb (one 1Gb and two 512Mb) DDR3 SDRAM. This board contains the Xilinx XC7A200T– FBG676 FPGA.

Prerequisites:

Hardware:

- HSFPX002 FPGA Module

- HSFPX00X Carrier Board

- Xilinx Platform Cable USB II JTAG debugger.

- USB A to USB Type C cable

Software:

- Vivado Design Suite with SDK installed.

Creating MicroBlaze based Hardware Platform for HSFPX002

The following steps will walk you through the process of creating a new project with Vivado and building a hardware platform with a MicroBlaze soft processor using an IP integrator. Numato Lab’s HSFPX002 FPGA Development Board is used in this example, but any compatible FPGA platform can be used with minor changes to the steps. Screenshots are added wherever possible to make the process easier for the reader.

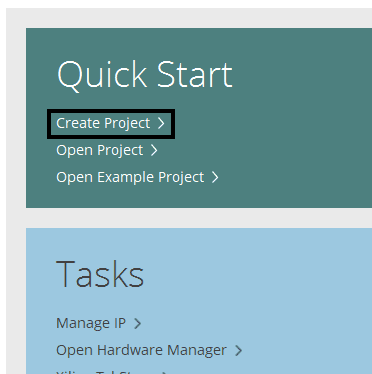

Step 1:

Open Vivado and select “Create Project” from the “Quick Start” section.

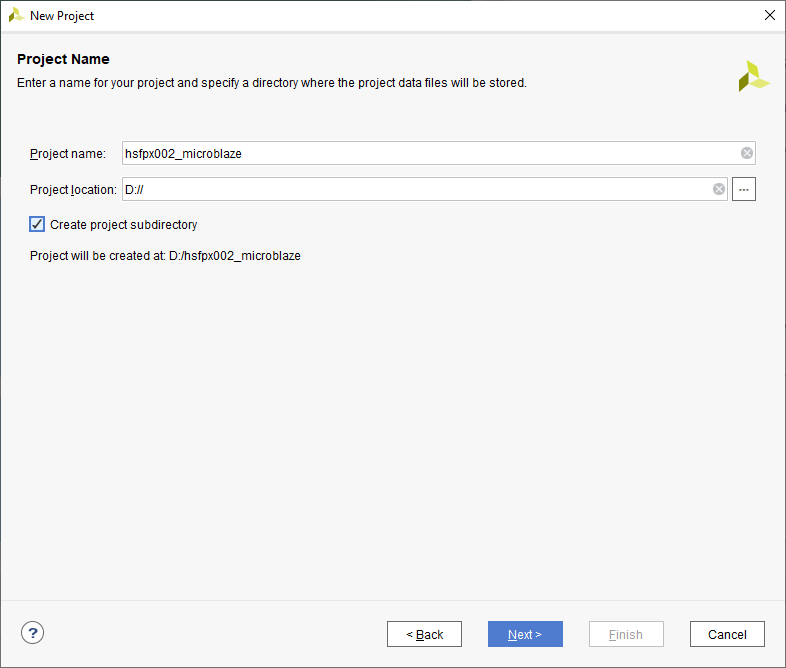

Step 2:

Click “Next” and then in the ‘Project Name’ tab, give an appropriate name and location then check the “Create project subdirectory” box and click “Next” till you see the ‘Default Part’ tab.

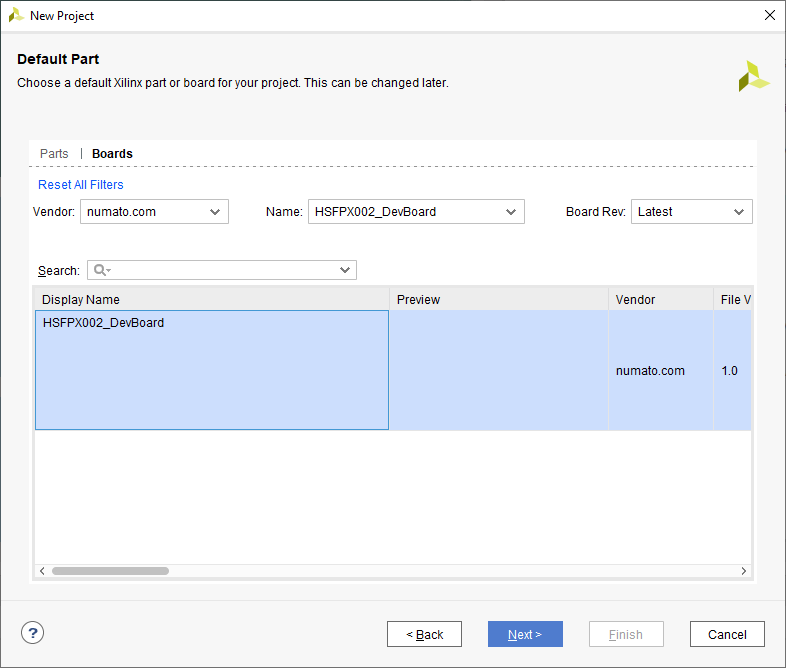

Step 3:

Select “Boards” from the “Default Part” tab, choose “numato.com” as Vendor. Select “HSFPX002_DevBoard” and click “Next”. If HSFPX002 is not listed, make sure the board support files are installed correctly. Click “Finish”. A new Vivado project will open with the selected settings.

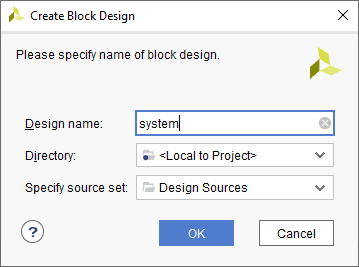

Step 4:

Click “Next” and then “Finish” to create the project. Click “Create Block Diagram” from the IP integrator tab on left, give a name for block design and click OK.

Step 5:

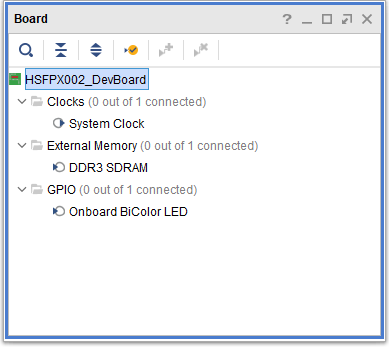

Select “Boards” in the “Block Design” block. The default peripherals available for the HSFPX002 Board will be displayed.

Step 6:

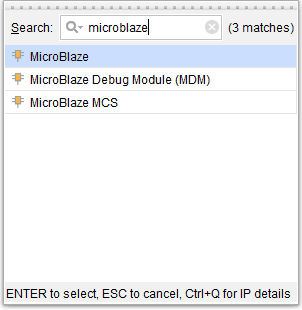

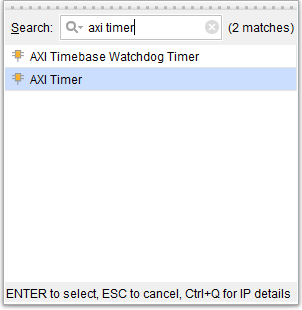

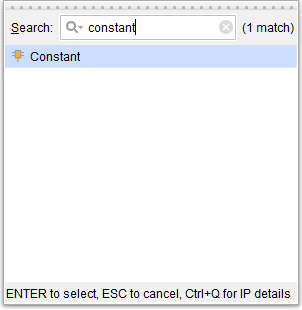

Add System Clock and DDR3 SDRAM to the design by double-clicking on the corresponding peripherals. In the design window, right-click and select “Add IP” from the popup menu. Search for ‘MicroBlaze’, ‘AXI timer’ and ‘Constant’ and add them to the design by double-clicking on them.

Step 7:

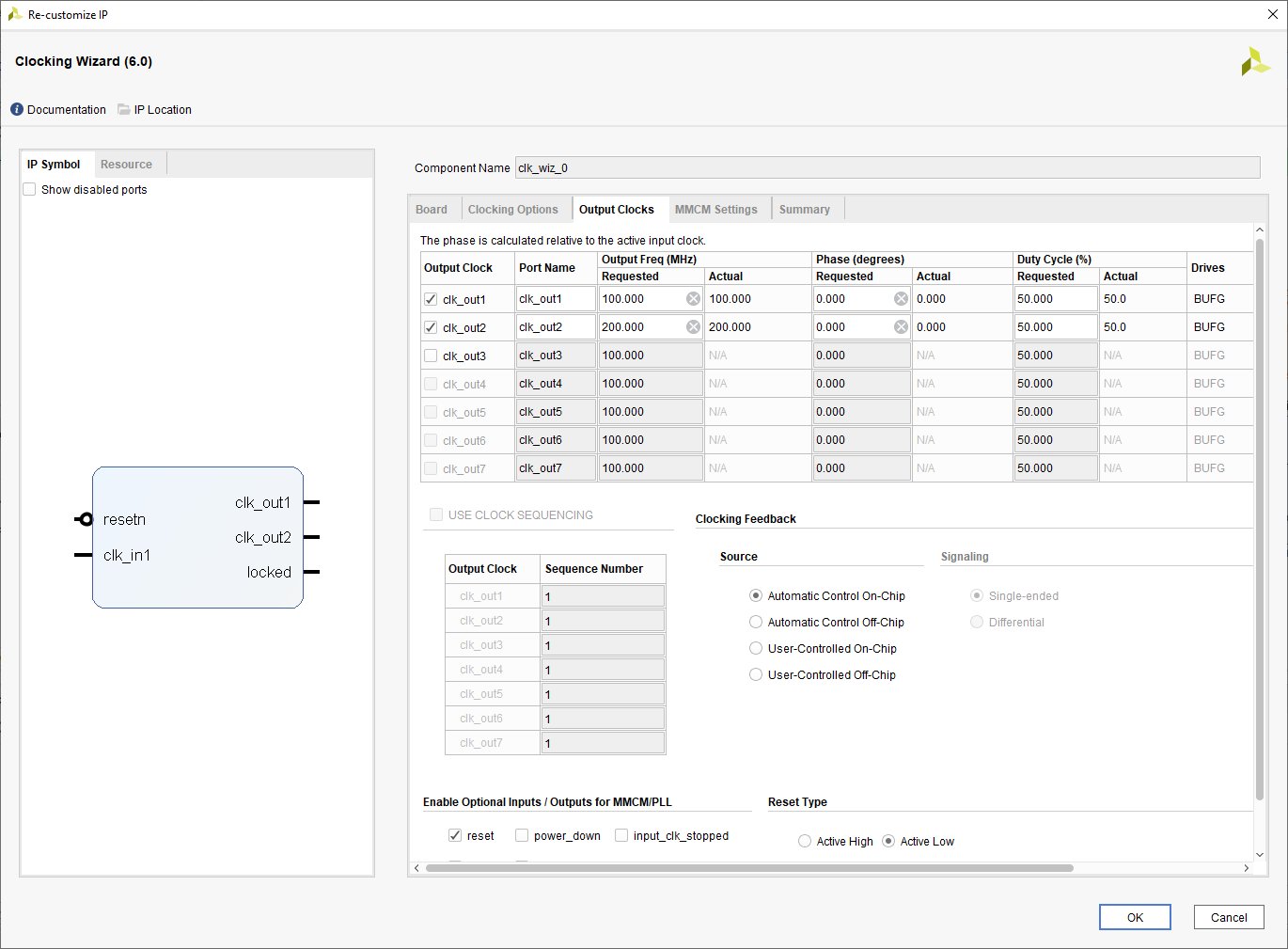

Double click on the Clock IP and make changes as shown below.

Step 8

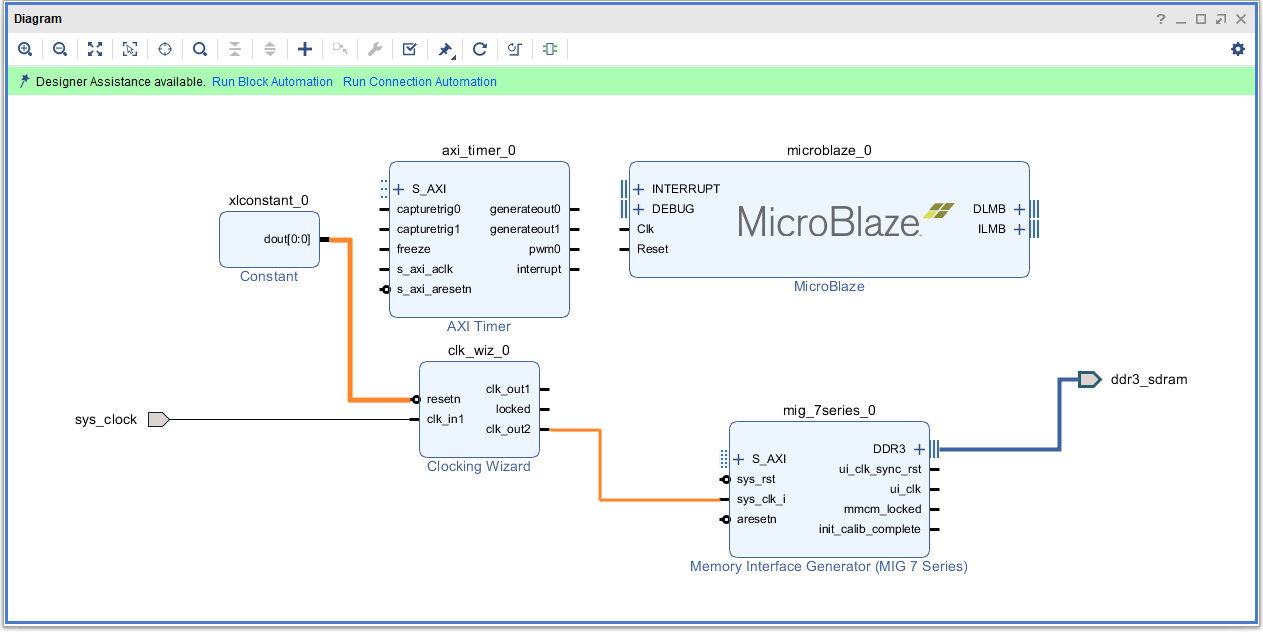

Remove the existing connection to ‘sys_clk_i’ of ‘MIG 7 Series’ and connect ‘clk_out2′ net on the ‘Clocking Wizard’ to ‘sys_clk_i’ of ‘MIG 7 Series’ block and also connect ‘resetn’ net on the ‘Clocking Wizard’ to ‘dout[0:0]’ of ‘Constant’ block as shown in the image below.

Step 9:

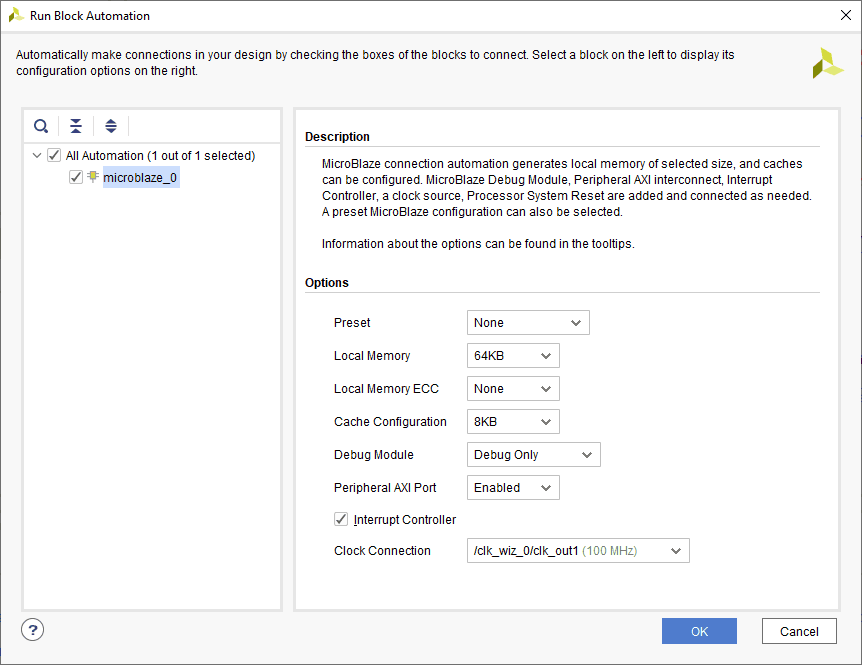

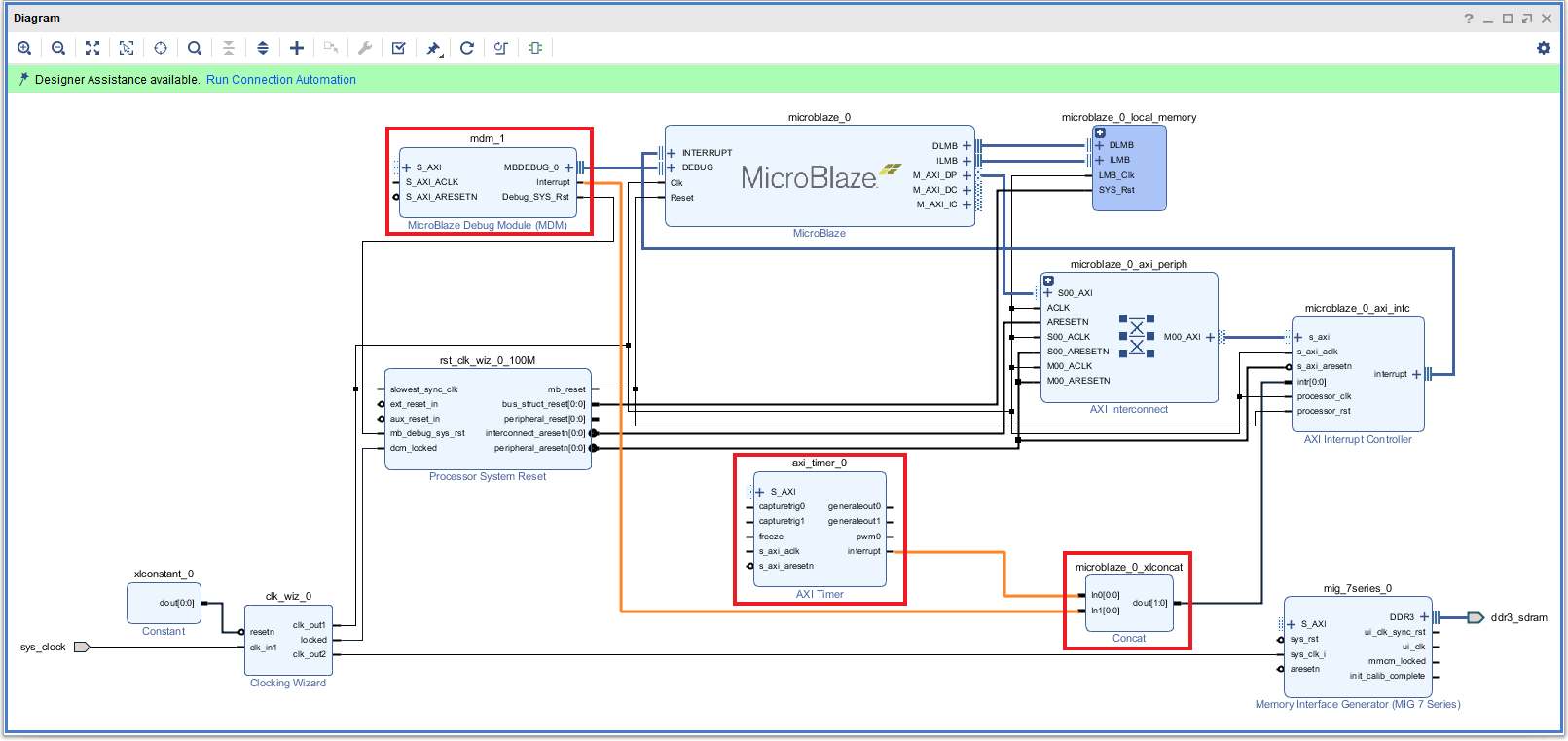

Click on “Run Block Automation” on the top left corner of the window to complete the design. Select the settings as shown in the below image. Click “OK” for Vivado to automatically configure the blocks for you. Once Block Automation is complete, click on “Run Connection Automation” so Vivado can connect the blocks to make a complete system.

Step 10:

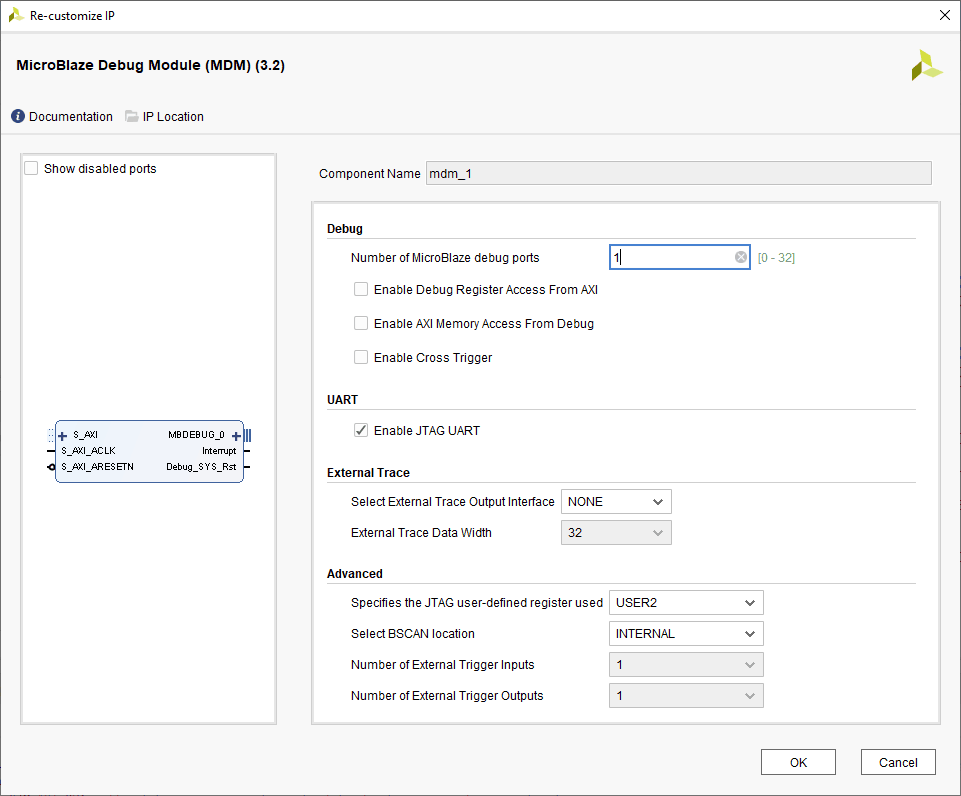

Now, double click on the ‘MicroBlaze Debug Module’ and in the Re-customize IP window, select the “Enable JTAG UART” option as shown in the image below.

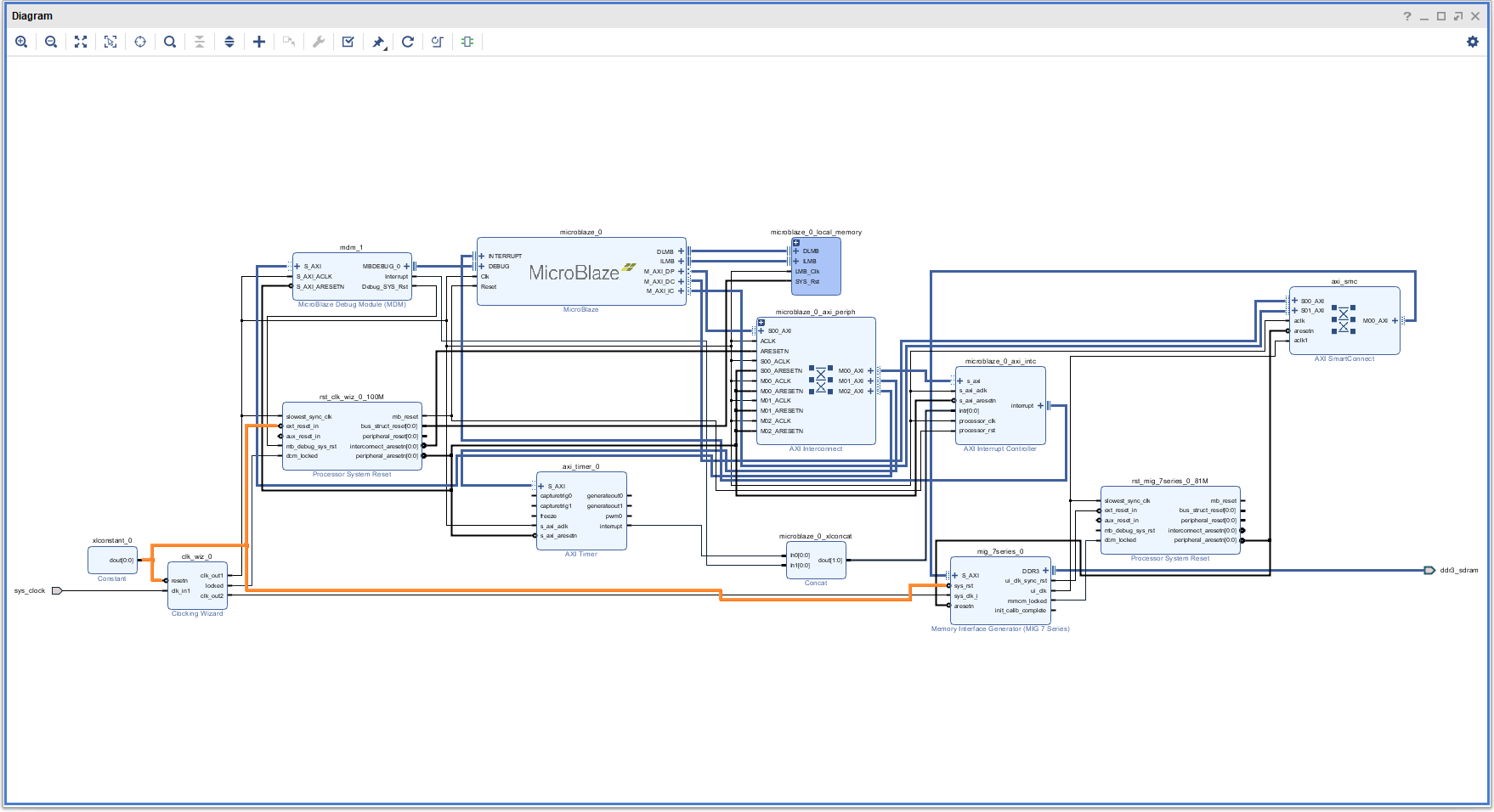

Then connect Interrupt output lines from AXI Timer and MicroBlaze Debug Module to the Concat block as shown in the picture below. The blocks in question are highlighted in red and the connections are highlighted in orange.

Now run connection automation once again for Vivado to complete the remaining connections.

After all the connections are made, remove the existing connection to ‘Processor System Reset’ and ‘MIG 7 Series’ and connect them to ‘resetn’ of ‘Clocking Wizard’ as shown in the image below.

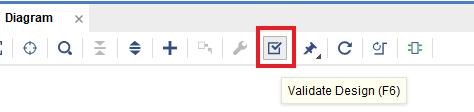

Validate the design to make sure there are no errors by clicking the “Validate Design” button present at the top of the Design window.

Step 11:

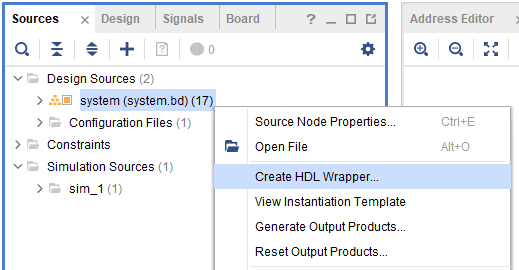

Save the design and then right-click on the design in the “Sources” window, select “Create HDL Wrapper” from the popup menu. Click “OK” on the window that appears to finish generating the wrapper.

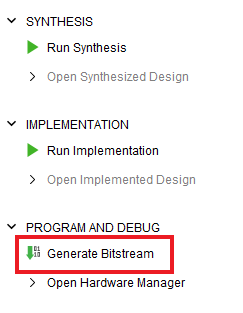

Step 12:

Now, click on “Generate Bitstream” under the “PROGRAM AND DEBUG” section to synthesis, implement and generate the bitstream.

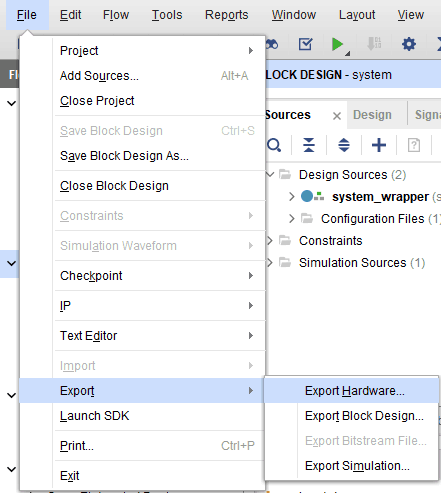

Step 13:

Now, that the implementation and generation of the bitstream are successfully completed, we need to export the hardware along with bitstream. Go to the “File” menu, select “Export->Export Hardware”. Select “Include bitstream” and click “OK”.

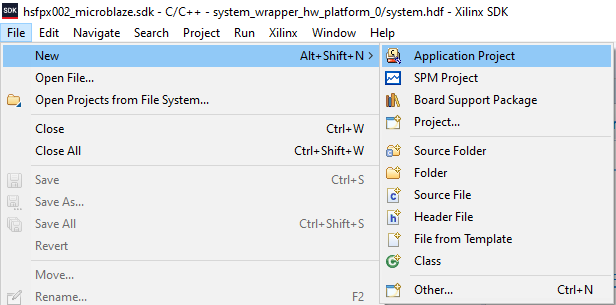

Step 14:

Launch SDK from the File menu. You may choose to use the local project directory as an SDK workspace or select another directory if appropriate. Once the SDK window appears, select the “New->Application Project” from the “File” menu. Type in a project name and click “Next” to select the “Hello World” template from the list of available templates.

Step 15:

Once the project is created, the SDK will automatically run a build. If that didn’t happen for any reason, run a build manually. Once the build is complete successfully, power up HSFPX002 FPGA Module and connect the Xilinx Platform USB cable and USB Type C cable for Serial debugging to the board.

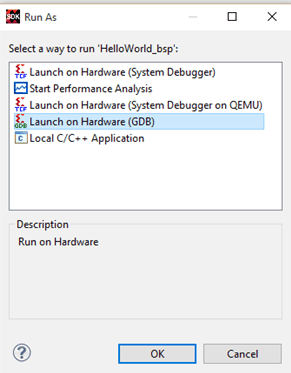

Step 16:

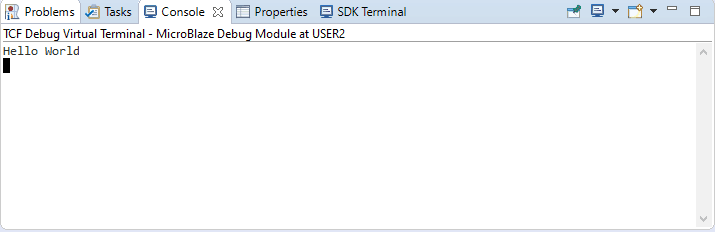

Program the board by selecting “Program FPGA” under the “Xilinx Tools” menu. Now run the application by clicking on the Run icon on the main toolbar. Select “Launch On Hardware (GDB)” when asked as shown in the image below.

If everything went well, the application running on the board should print “Hello World” over the USB UART and should be displayed on the Console terminal as shown in the image below.