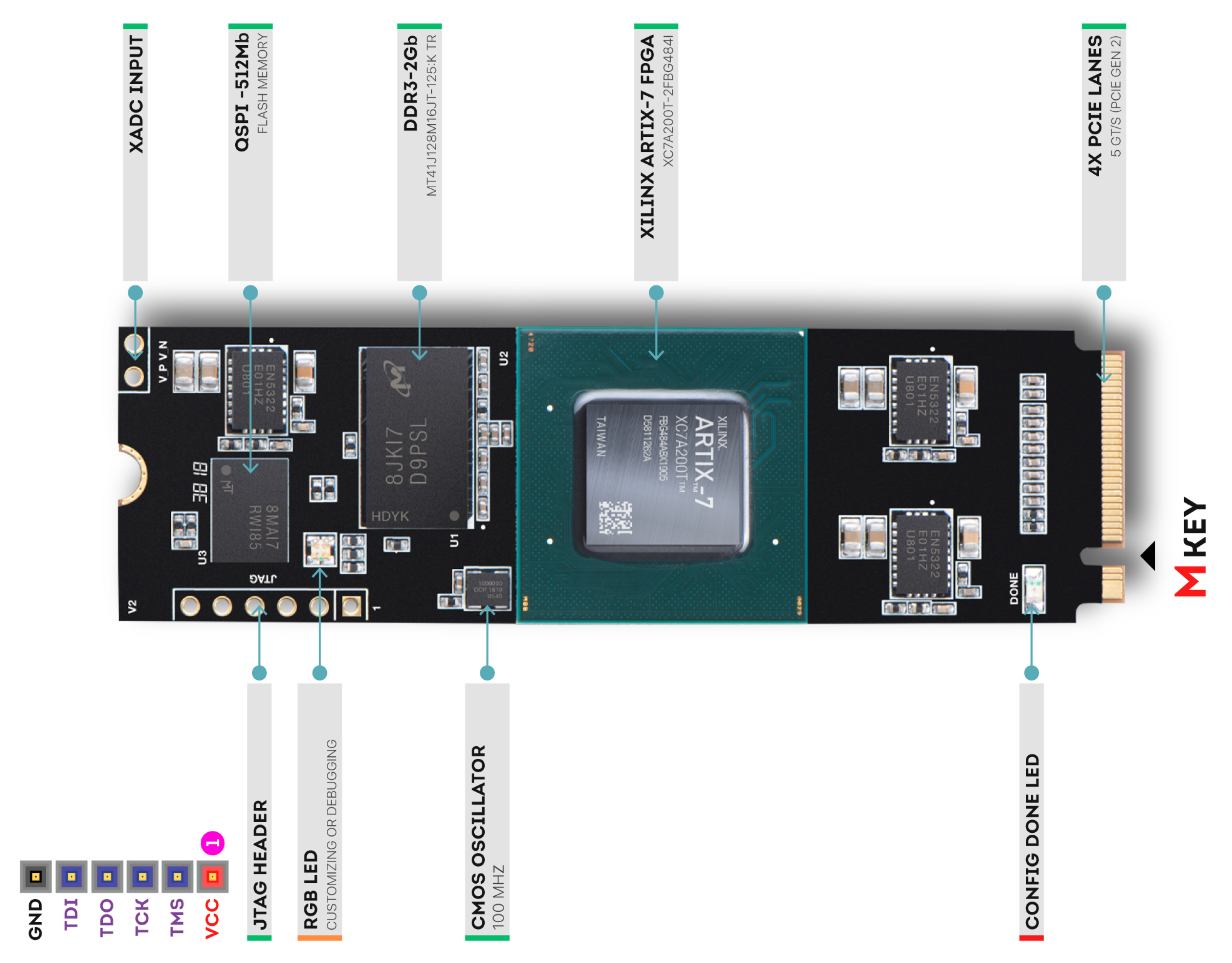

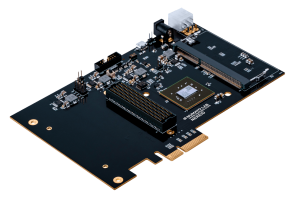

Aller A7 FPGA Board with M.2 Interface

Request For QuoteWanna Customize? Drop Us A Line!

Aller A7 is specifically designed for the development and integration of FPGA-based accelerated features into other larger designs, it can be used with laptops, desktops, and servers featuring standard 2280 M.2 form factor M-key slot.

Aller A7 is an easy-to-use M.2 form-factor FPGA Development Board featuring AMD Artix-7 FPGA with x4 PCIe Gen2 lanes on M.2 M-Key interface, Trusted Platform Module (TPM AT97SC3205), 2Gb DDR3 SDRAM and 512 Mb QSPI Flash Memory.

Nowadays, most of the new laptops come with M.2 M-key slots for NVMe storage modules and Aller can be seamlessly used with those slots. Open source PCI Express IP cores such as litepcie make the development of PCIe designs very cost-effective. The M.2 M-Key provides up to 4x PCIe lanes, each running at 5 GT/s (PCIe Gen 2) on Aller.

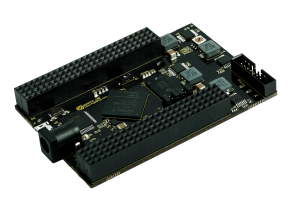

Note: Heat sink is mandatory when using Aller with heavy designs. Aller A7 ships with a standard heat sink which should be sufficient for most use cases.

Please refer to the Aller A7 User Manual for detailed information on temperature and heat dissipation.

Features

- Device: AMD Artix 7 FPGA (XC7A200T-2FBG484I)

- DDR3: 2Gb DDR3 ( MT41J128M16JT-125:K TR )

- 4 lane PCIe Gen2 (5 GT/s)

- Flash memory: 512 Mb Quadbit SPI flash memory (S25FL512SDSBHV210/IS25LP512M-RHLE)

- JTAG header for programming and debugging

- 100 MHZ CMOS oscillator

- 1 x Trusted Platform Module (AT97SC3205)

- M.2 Connector Interface, M-Key

- Powered from M.2 connector

- 1 RGB LED for custom use

Applications

- Product Prototype Development

- Accelerated computing integration

- Development and testing of custom embedded processors

- Signal Processing

- Memory Intensive FPGA development

- Educational tool for Schools and Universities

- High Hash Rate calculations for Blockchain technologies such as Bitcoin and Ethereum

- Offloading computationally intensive algorithms to FPGA

- Machine Learning and Artificial Intelligence

Downloads

Specifications

| Attribute | Value |

|---|---|

| Weight | 0.6 lbs |

| Dimensions | 5 × 3 × 1 in |

| Product Dimensions - without heat sink | 3.15 x 0.90 x 0.18 in |

| FPGA | |

| Configuration Options | |

| Memory | |

| Non-Volatile Configuration Storage | 1Gb flash memory |

| Total Number of GTP | 4 (PCIe Gen 2, 4 lanes) |

| Junction Temperature Range | 0-90 degrees Celsius |

| Power Supply | 3.3V from M.2 connector (M-Key) |

| Primary Clock Frequency | |

| Package Contents | |

| HTS | 8542.39.0001 |

| ECCN | 3A991.d |