XO-Bus Lite Host Interface IP for Xilinx FPGAs (Retiring soon)

NOTE: We are about to release a new SDK that will replace XO Bus Lite. Please send us a message to [email protected] to keep you in the notifications list for the upcoming tools.

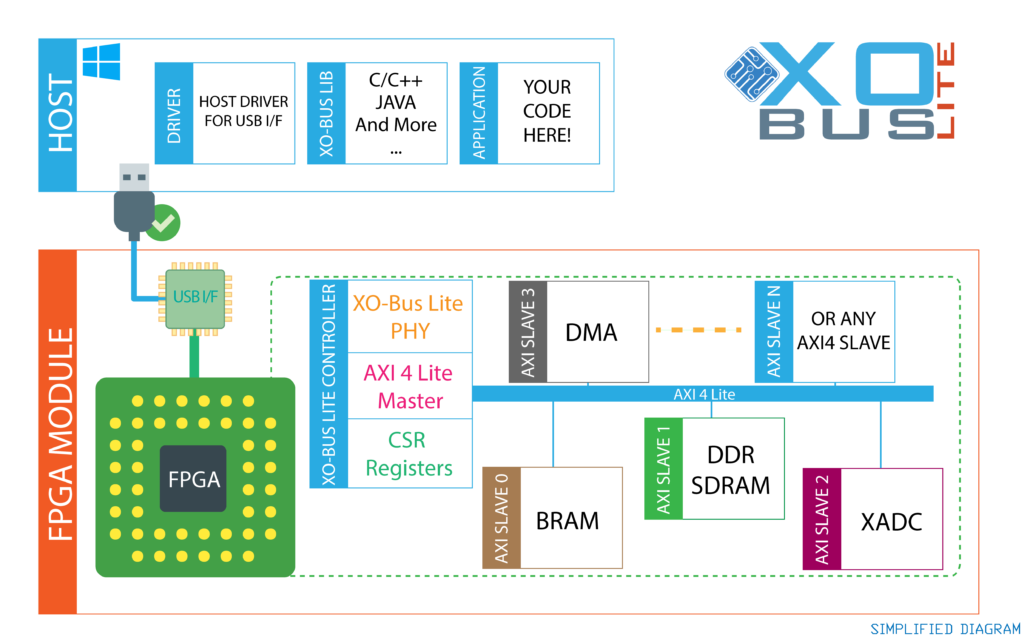

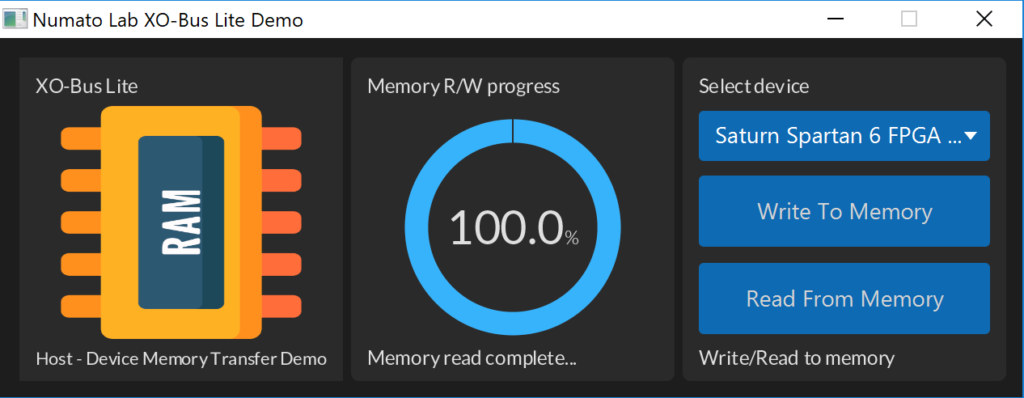

XO-Bus Lite is a framework designed to make communication with Numato Lab’s FPGA boards easier from a host. XO-Bus Lite accelerates the development by providing an intuitive way of transferring data into and out of the FPGA and attached memory devices such as DDR SDRAM. This framework acts as a standard AXI 4 (Lite) Memory Mapped Master, and it can control any AXI4 compliant slaves. This makes it very easy to use existing AXI 4 infrastructure provided by Xilinx Vivado, ISE, and XPS. This feature itself makes XO-Bus Lite Framework very powerful. Users can use most if not all IP cores that support the AXI interface and read/write to memory and memory-mapped registers on the devices directly from host PC. There is no need for any microprocessor (such as Microblaze) to mediate the data transfer, though XO-Bus Lite can also work alongside Microblaze or any other AXI Master. This gives users a high degree of flexibility in their designs, faster time to market while being a low-cost solution.

Features

- Industry-standard AXI 4 (Lite) support

- Possibility of using a vast array of existing AXI 4 based IPs

- IP packages for Xilinx Vivado and XPS making design a breeze

- Host SDK with intuitive APIs for various languages

- Demo apps to get you started quickly

Available host libraries

Supported devices

- Saturn – Spartan 6 FPGA Development Board with DDR SDRAM

- Neso – Artix 7 FPGA Development Board

- Skoll – Kintex 7 FPGA Development Board

Supported host protocols

- USB 2.0 through built-in USB2.0 – FIFO bridge

Supported Operating Systems

- Windows 64 bit (Windows 32 bit and Linux support coming soon..)

XO-Bus Lite software stack contains the following components

- Target PHY and controller implementation in netlist format

- Packaged IP for Xilinx Vivado and XPS

- Sample projects for Xilinx Vivado, ISE, and XPS

- Host libraries for direct API access

- Language-specific libraries (Java etc..)

- Sample host applications demonstrating API usage

Currently available host APIs (C/C++)

XO_STATUS GetLibInfo(PTR_LIB_INFO ptrLibInfo);

XO_STATUS GetBoardCount(DWORD *ptrBoardCount);

XO_STATUS GetBoardInfo(DWORD boardIndex, PTR_BOARD ptrBoard);

XO_STATUS Open(PTR_BOARD ptrBoard);

XO_STATUS Close(PTR_BOARD ptrBoard);

XO_STATUS Ping(PTR_BOARD ptrBoard);

XO_STATUS ReadCSR(PTR_BOARD ptrBoard, UCHAR regIndex, DWORD *data);

XO_STATUS WriteCSR(PTR_BOARD ptrBoard, UCHAR regIndex, DWORD data);

XO_STATUS Read(PTR_BOARD ptrBoard, UINT address, UINT length, void *buf);

XO_STATUS Write(PTR_BOARD ptrBoard, UINT address, UINT length, void *buf);

Specifications

| Attribute | Value |

|---|---|

| Supported Operating Systems | Windows® 8 x64, Windows® 8.1 x64, windows® 10 x64 |

| Minimum Hardware Requirements | 2 Core x64 CPU, 8GB Memory, 300MB Disk Space |