In this project, we will showcase the process of implementing an LPDDR4 read and write on the Eagle Core PolarFire SoC System on Module (SoM).The EagleCore PolarFire SoC SOM is equipped with 4GB of LPDDR4 memory (MT53D1024M32D4DT-053), which provides efficient and high-speed memory access for system operations, making it ideal for memory-intensive applications

Prerequisites:

Hardware:

- EagleCore PolarFire SoC SOM

- FlashPro 6/5 programmer

- USB A to USB Type C cable

- 5V-12V DC Power Supply

Software:

- MSS Configurator (v2022.3)

- Libero SoC IDE (v2022.3)

- Softconsole (v2022.2)

Implementation:

PolarFire SoC MSS Configurator

Libero makes use of an external application called the PolarFire SoC MSS Configurator to generate and set up the Microcontroller Subsystem (MSS) for the PolarFire SoC. Afterward, this configured component is integrated into the SmartDesign.

Step 1:

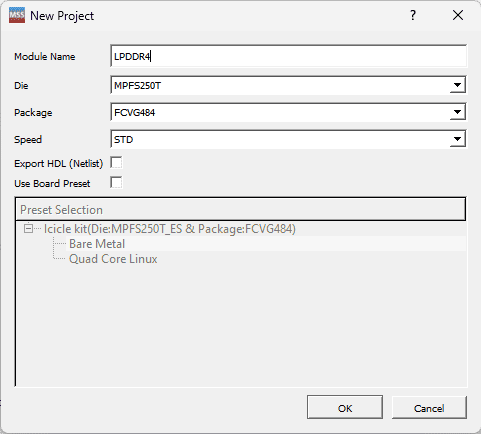

Open the PolarFire SoC MSS Configurator application. Once the application has launched, you should create a new project and give the appropriate name for the Configurator.

Step 2:

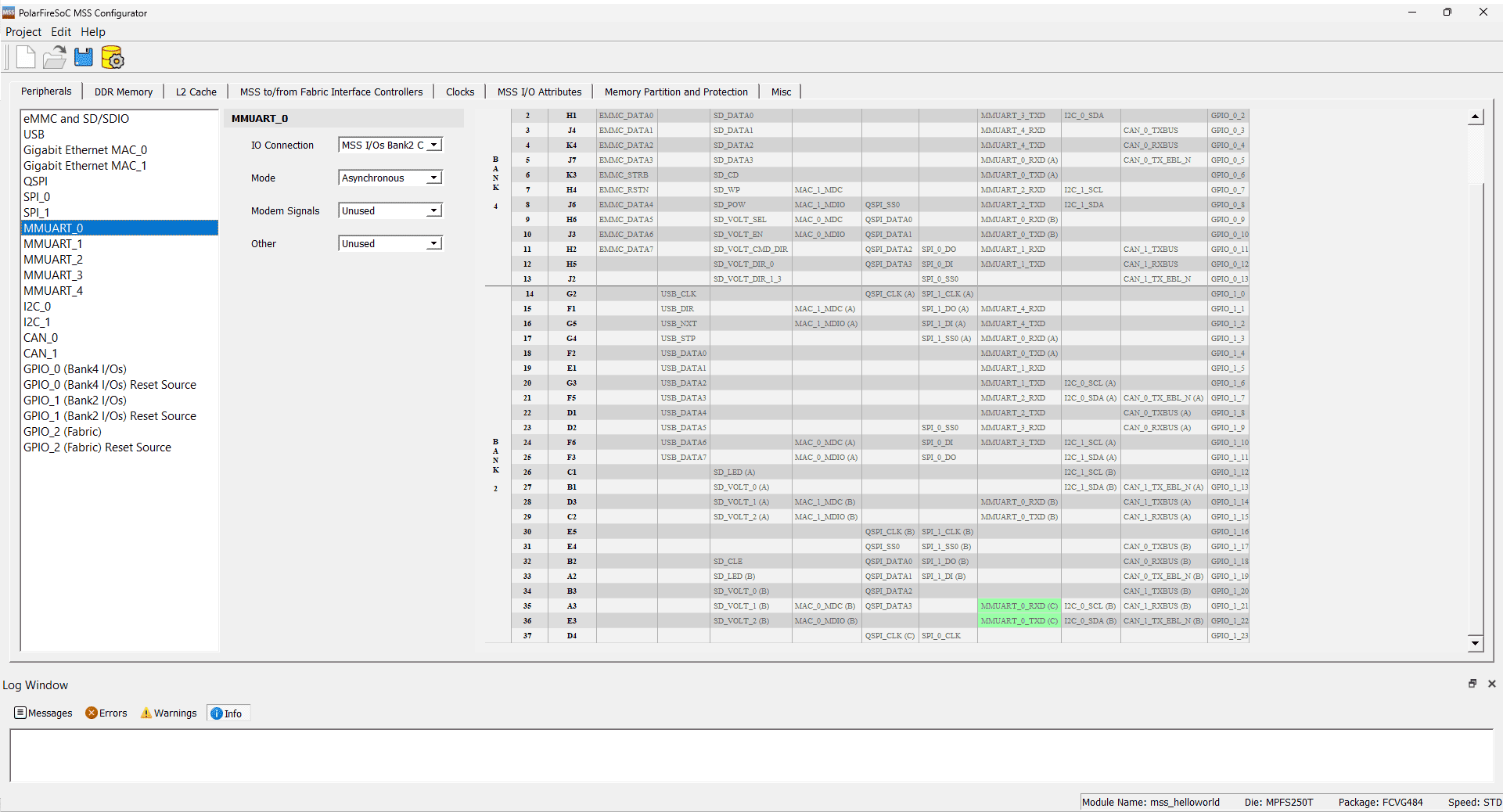

Navigate to the “Peripheral” tab and choose “MMUART_0” configure its settings according to the provided image below.

Step 3:

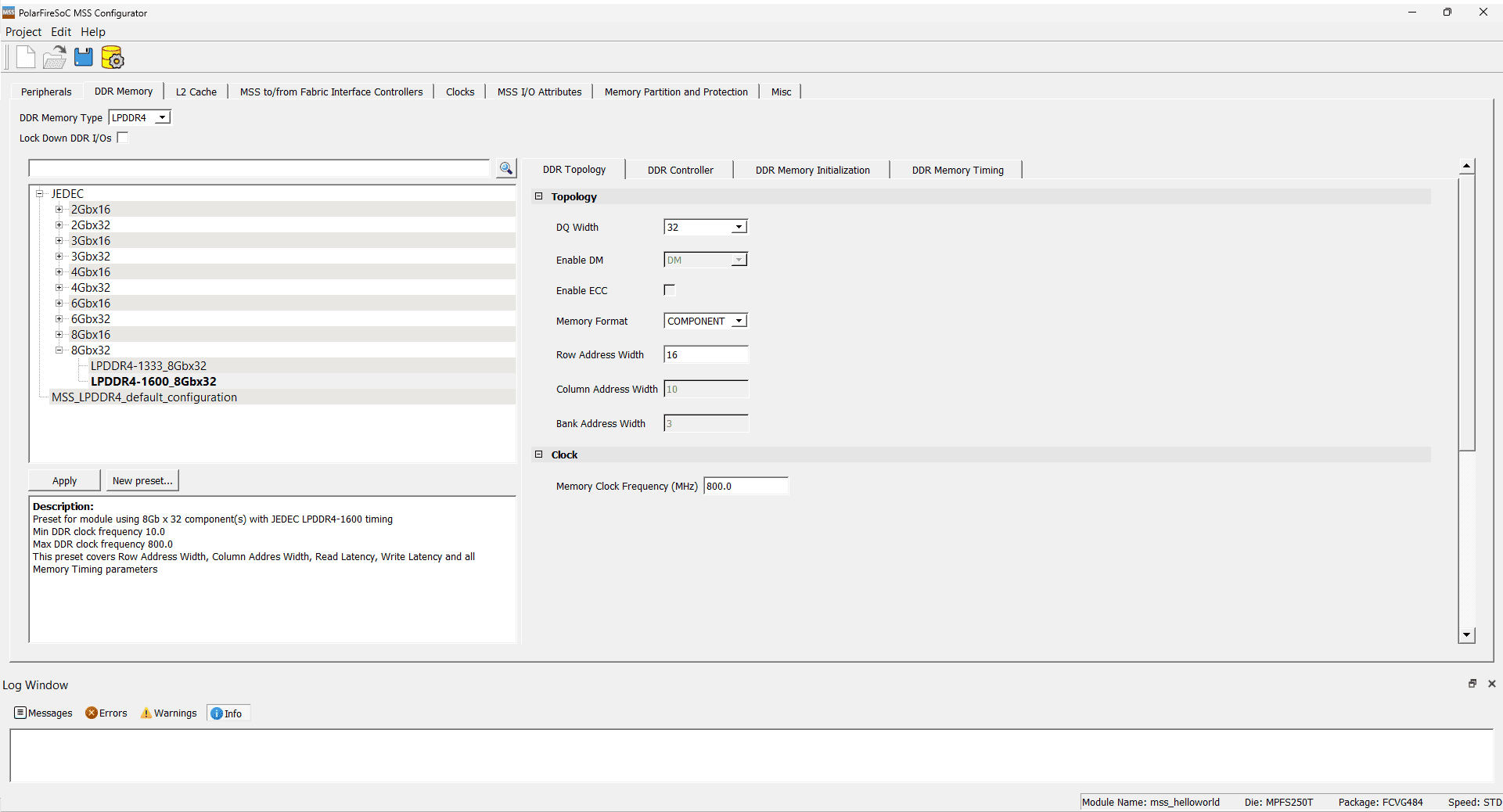

Now, under the “DDR Memory” tab, select “LPDDR4” as the “DDR Memory Type.” Choose “LPDDR4-1600_8Gbx32” as the JEDEC Configuration. Please maintain the default values for the “DDR Topology,” “DDR Controller,” “DDR Memory Initialization,” and “DDR Memory Timing” tabs.

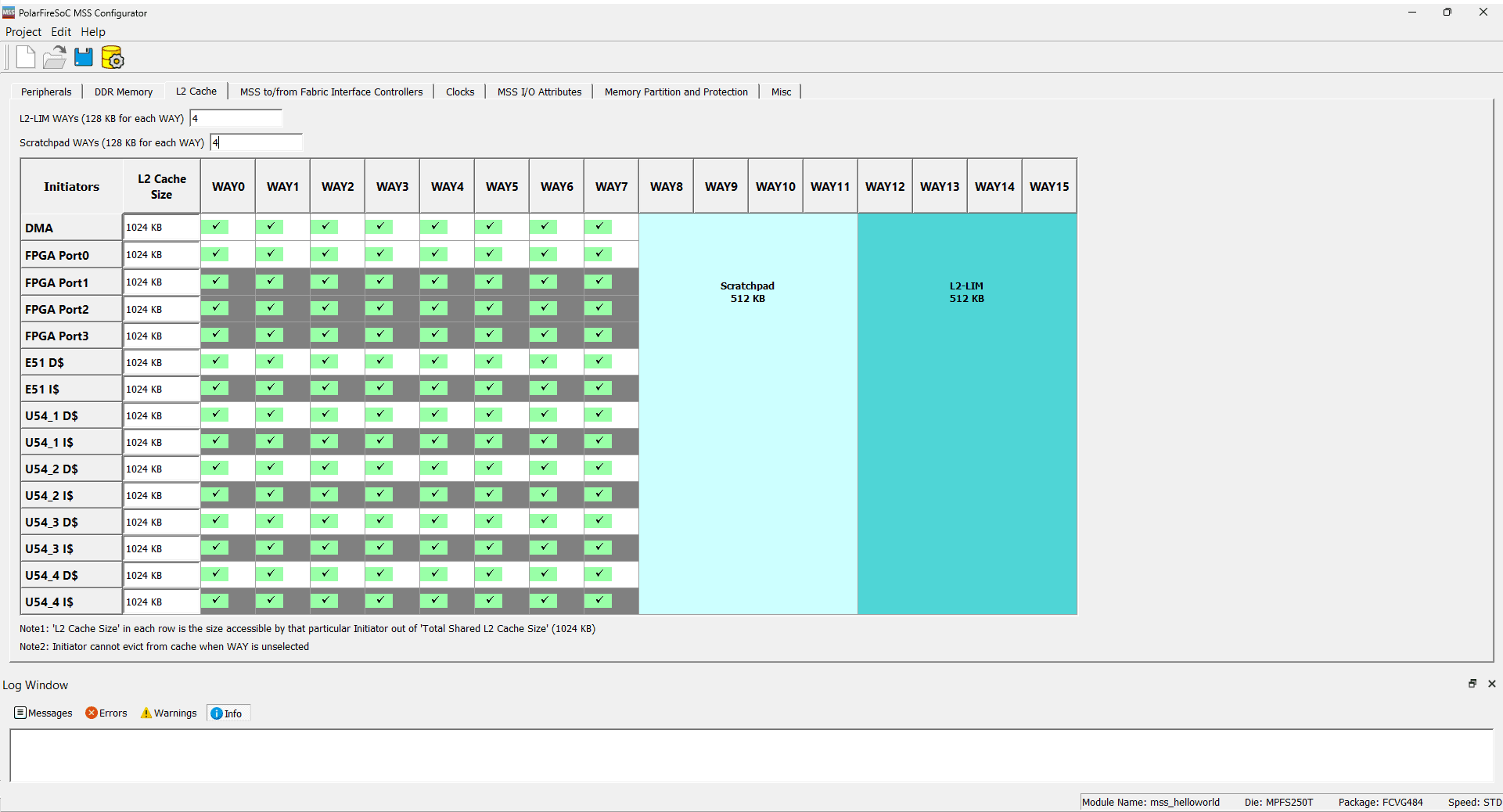

Step 4:

Now, under the “L2 Cache” tab, set L2-LIM WAYs to 4 and Scratchpad WAYs to 4.

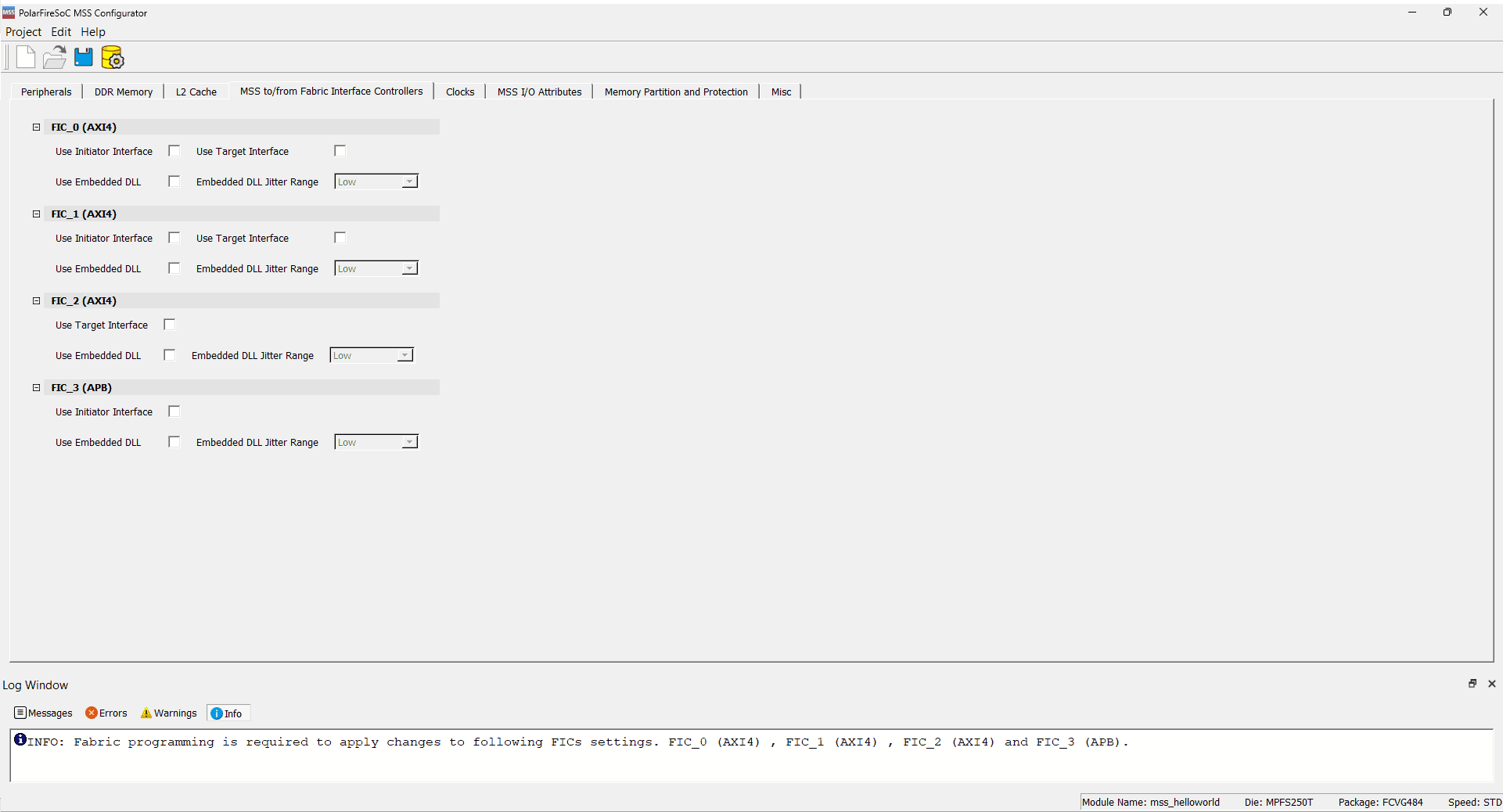

Step 5:

Disable all of the FIC interface under the MSS to/from fabric Interface Controller Tab.

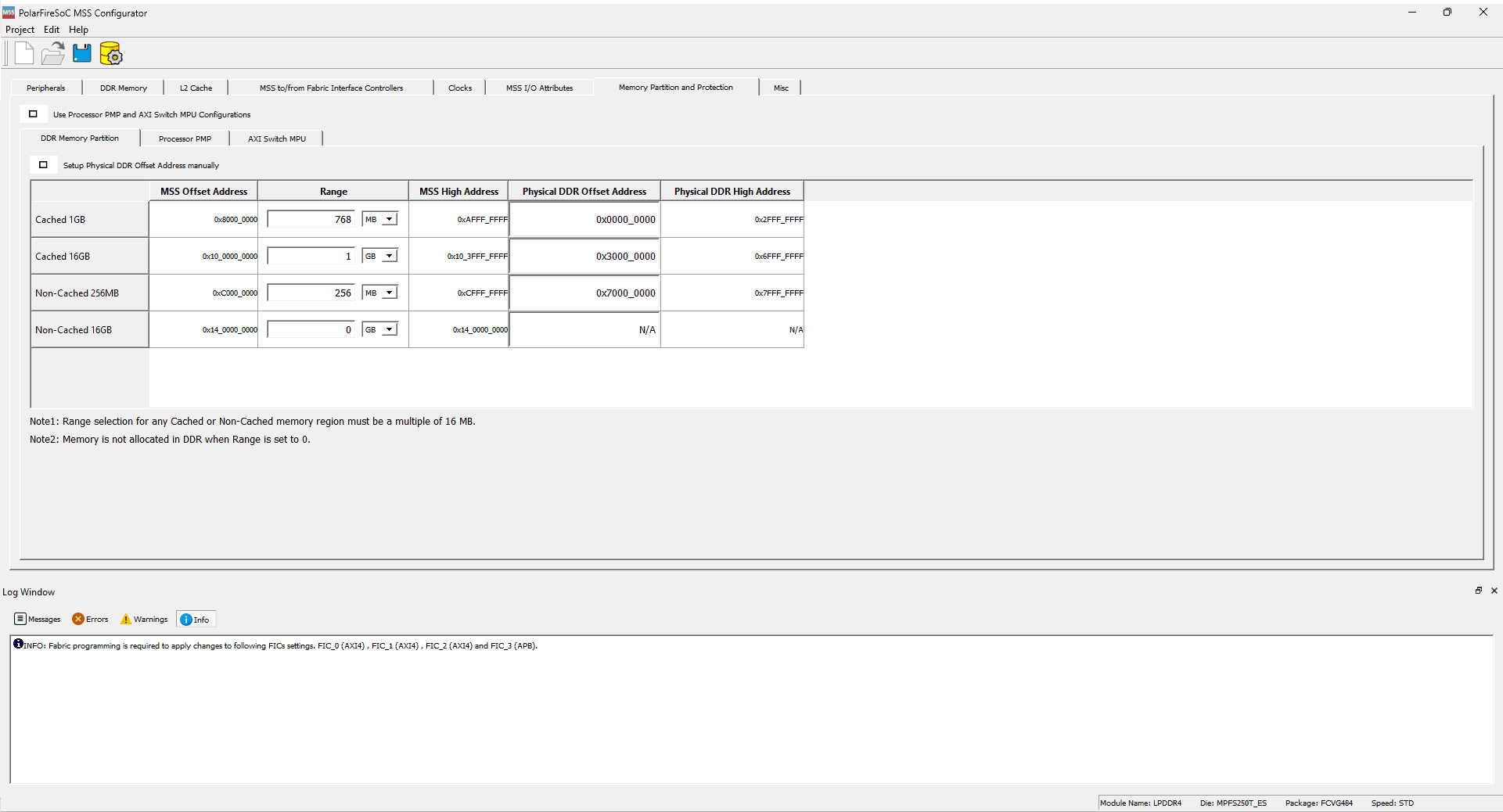

Step 6:

Now under the Memory Partition and Protection tab, give the Cached 16GB Range value as 1GB

Step 7:

Now generate the output by clicking on the ![]() Icon or Project -> Generate. Provide a suitable location where the files should be saved.

Icon or Project -> Generate. Provide a suitable location where the files should be saved.

Files included:

- LPDDR4.cfg

- LPDDR4.cxz

- LPDDR4_mss_cfg.xml

- LPDDR4_Report.html

Libero SoC

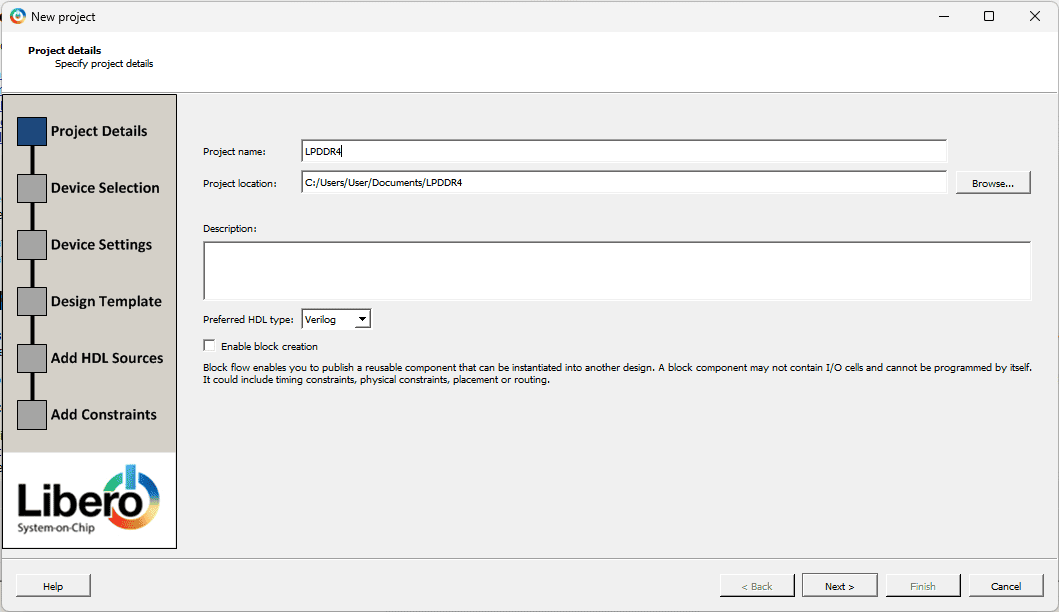

Step 8:

Open Libero SoC, then create a new project by clicking on “Project” > “New Project.” Given the Project name and Project location Click Next.

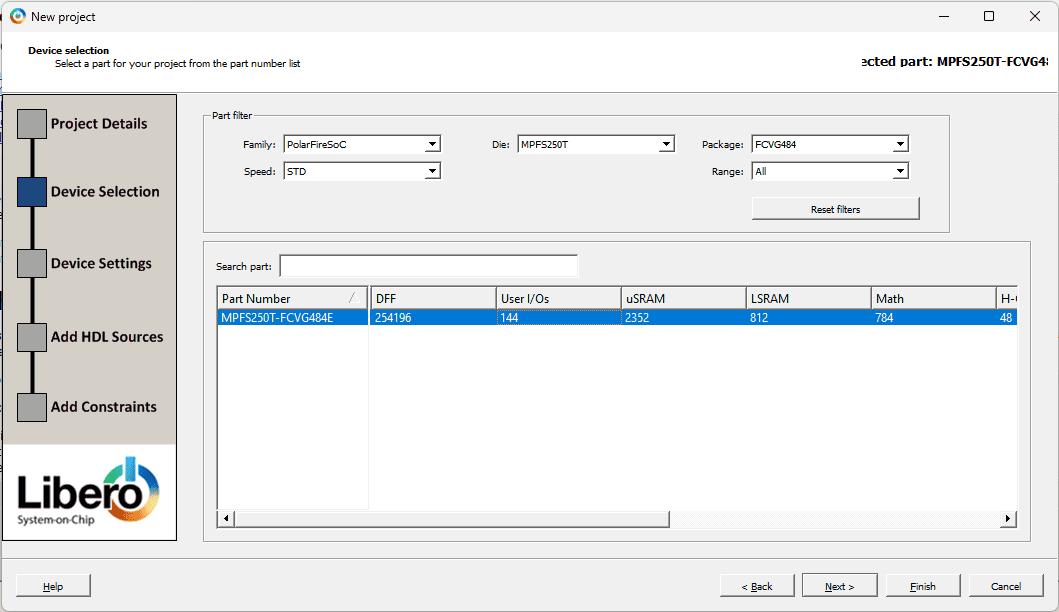

Step 9:

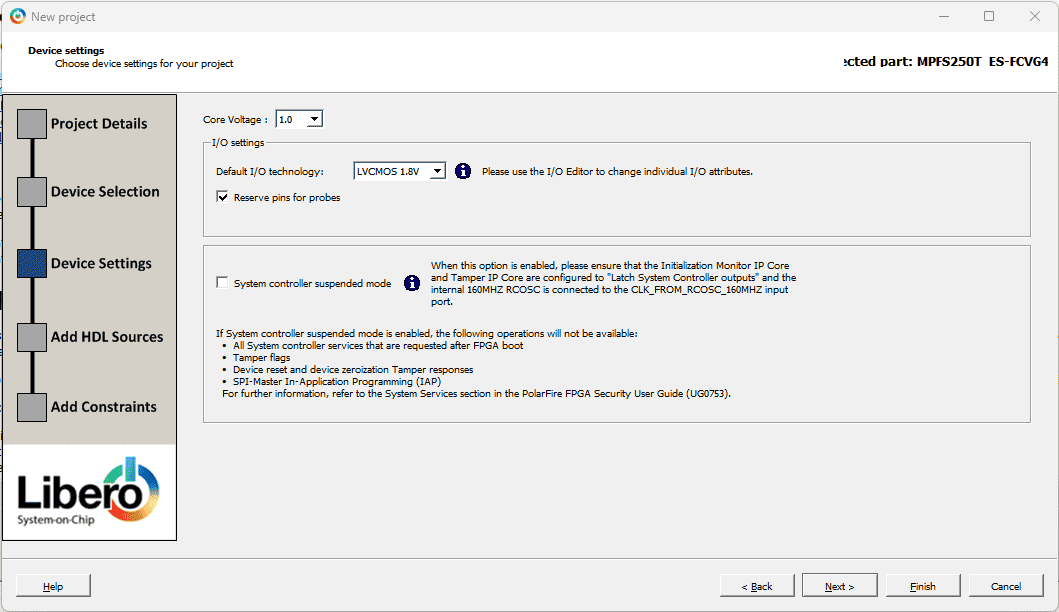

Step 10:

In the Device setting window select the Core Voltage as 1.0V and Default I/O Technology as LVCMOS 1.8V. Click Next.

As there’s no need to include HDL source or Constraint files directly, proceed by clicking Finish.

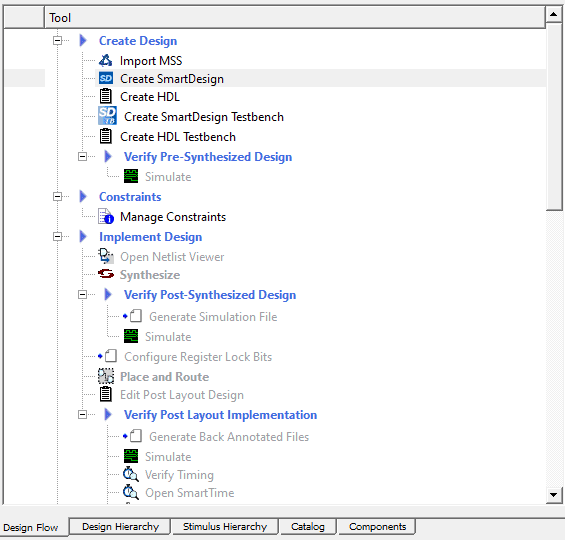

Step 11:

Once the New Project Wizard opens, double-click on the Create SmartDesign (![]() ) located under “Create Design” in the Design Flow tab and give proper naming.

) located under “Create Design” in the Design Flow tab and give proper naming.

Step 12:

Within the Design Flow, it’s necessary to import the MSS configuration, specifically the .cxz file. Double-click on Import MSS under Create Design. Specify the path where the MSS configurator .cxz file is saved.

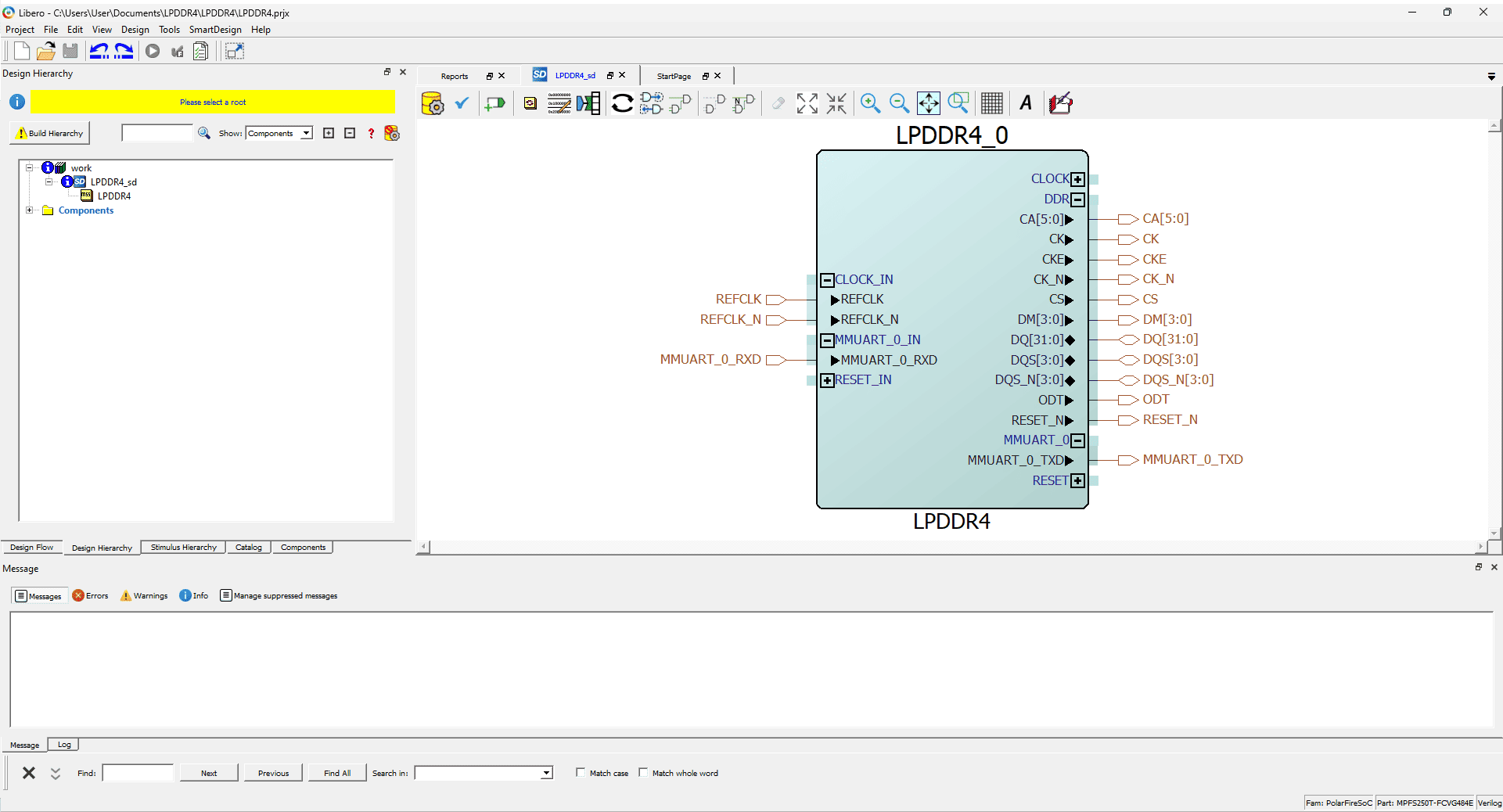

In the Design Hierarchy Tab, you’ll find the MSS component. Next, open the SmartDesign and instantiate the MSS component in it.

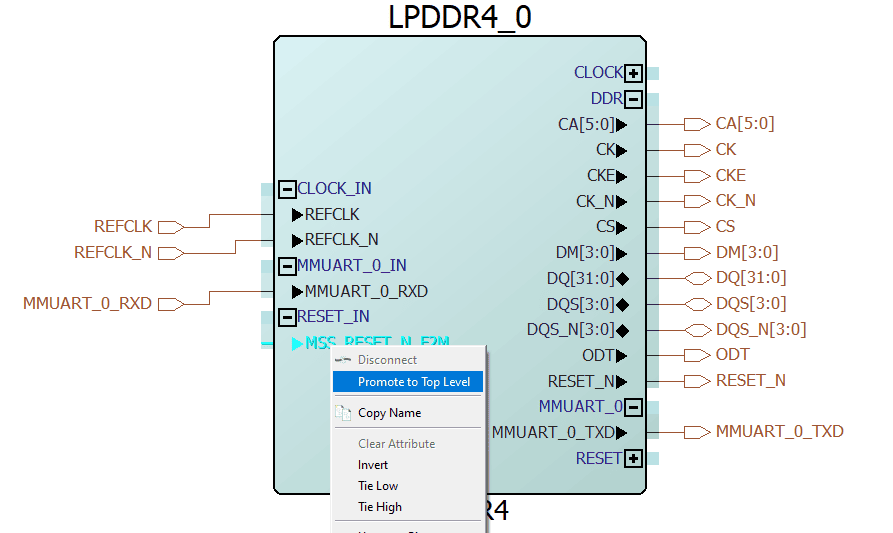

Step 13:

After instantiating the MSS component within the SmartDesign, promote MSS_RESET_N_F2M to the top level.

Step 14:

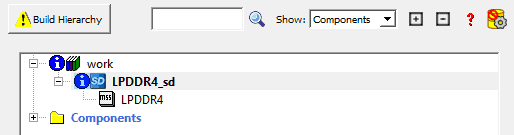

Now, click on “Generate Component (![]() )” and ensure there are no detected errors. Set the SmartDesign as the root and click on “Build Hierarchy.”

)” and ensure there are no detected errors. Set the SmartDesign as the root and click on “Build Hierarchy.”

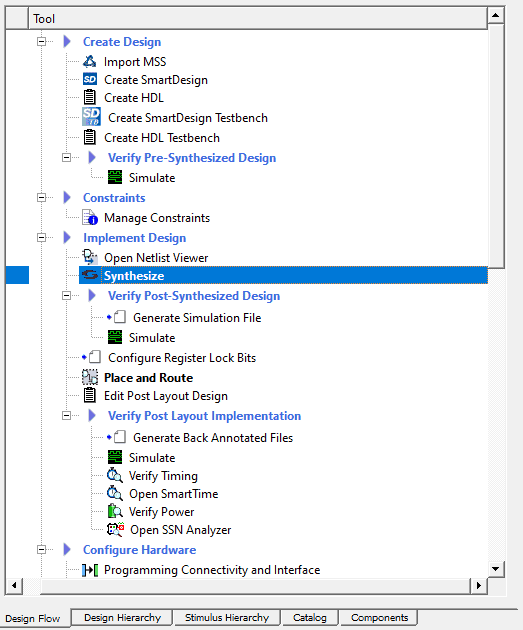

Step 15:

Proceed by clicking on “Synthesis” under “Implement Design” in the Design Flow tab.

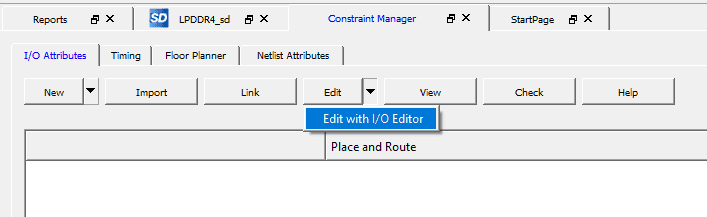

Step 16;

After the synthesis process is finished, double-click on “Manage Constraints” under the “Constraint” option. Then, select “Edit” under the I/O Attribute Tab within the constraint manager window, and choose “Edit with I/O Editor“.

Step 17:

Upon opening the I/O Editor window, you’ll see the complete set of constraints, which includes LPDDR4 and UART pins. You should focus on setting the constraint solely for the MSS reset and connecting the MSS Reset pin to H7. After making these adjustments, save and close the I/O Editor window.s

Step 18:

Now click Generate Bitstream, and wait for the bitstream to be generated.

SoftConsole

Import /driver-examplemssmpfs-hal/mpfs-hal-ddr-demo example project to a folder from PolarFire SoC GitHub.

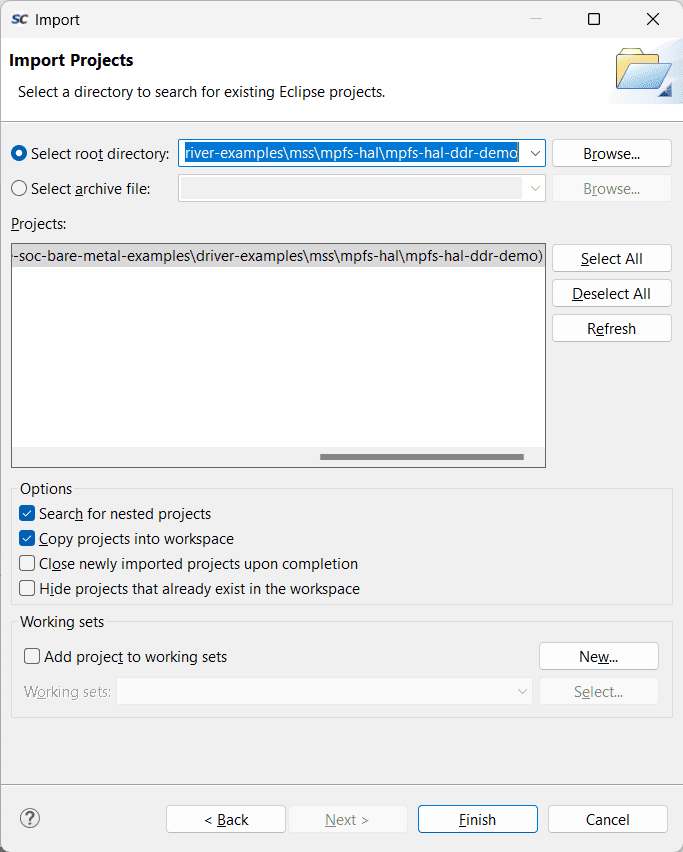

Step 19:

To import the UART bare metal project into the new SoftConsole project, go to the “Import projects” option. In the Select window, choose the import wizard as the “Existing projects into Workspace“. Click Next.

In the import project window, specify the root directory of the bare metal project. Click Finish.

Step 20:

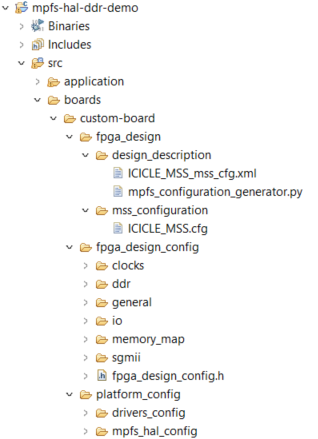

As the bare metal project was originally designed for the PolarFire SoC development kit, it’s necessary to replace the board XML file with the new XML file generated using the MSS configurator. To complete this, access the specified path and replace the file. Alternatively, you can create a new folder that consolidates all folders, including “fpga_design,” “fpga_design_config,” and “platform_config.” You can copy these files from the Icicle Kit bare metal project. It’s not essential to include clock, DDR, etc., files inside the “fpga_design_config” folder, as they will be automatically generated once you build the project with your XML file.

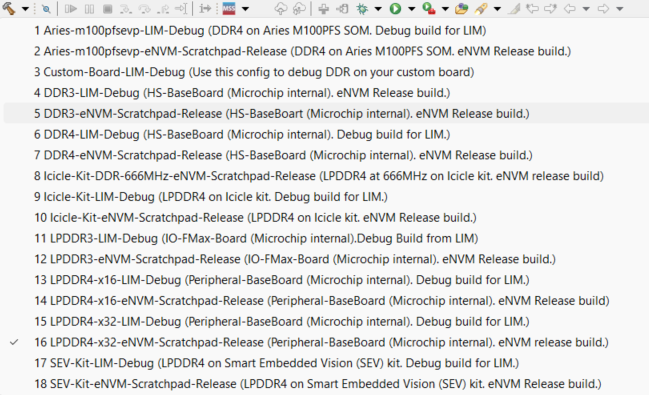

Step 21:

After completing the modifications for the custom board, proceed to build the project by selecting “LPDDR4-x32-eNVM-scratchpad-release”

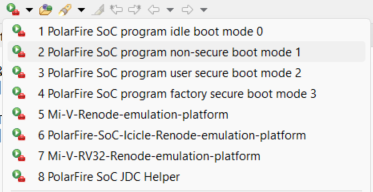

Step 22:

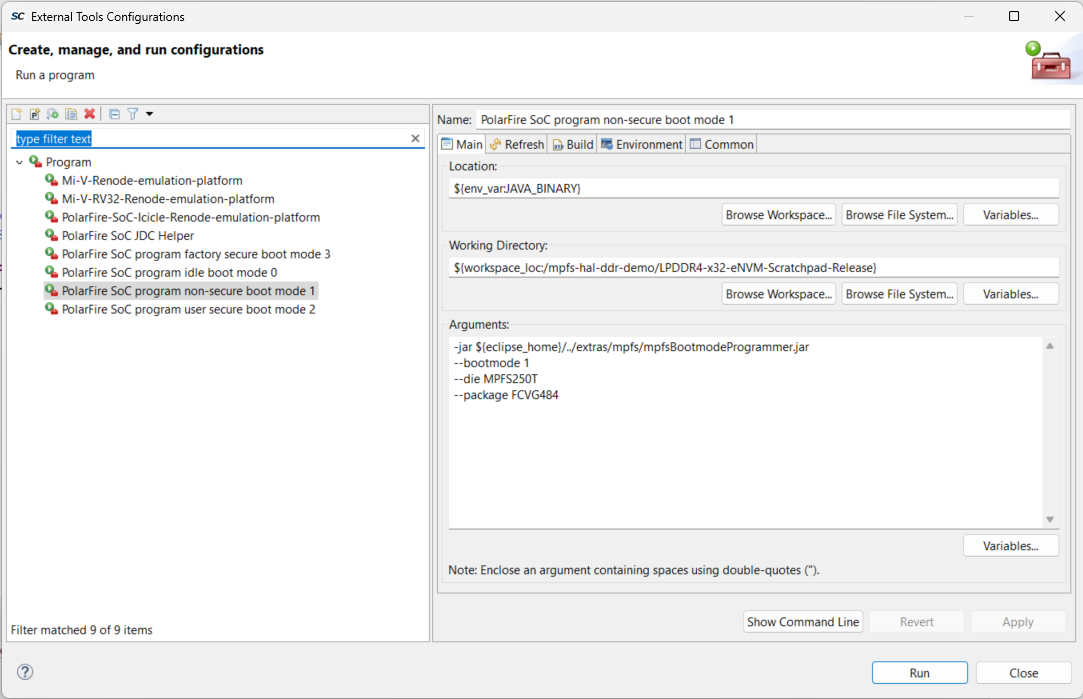

Once the project is built, you can program the board by connecting the FlashPro 5/6 to the board, powering it, and selecting the configuration option as “2 PolarFire SoC program non-secured boot mode 1”

Make sure to change the configuration for MPFS250T,

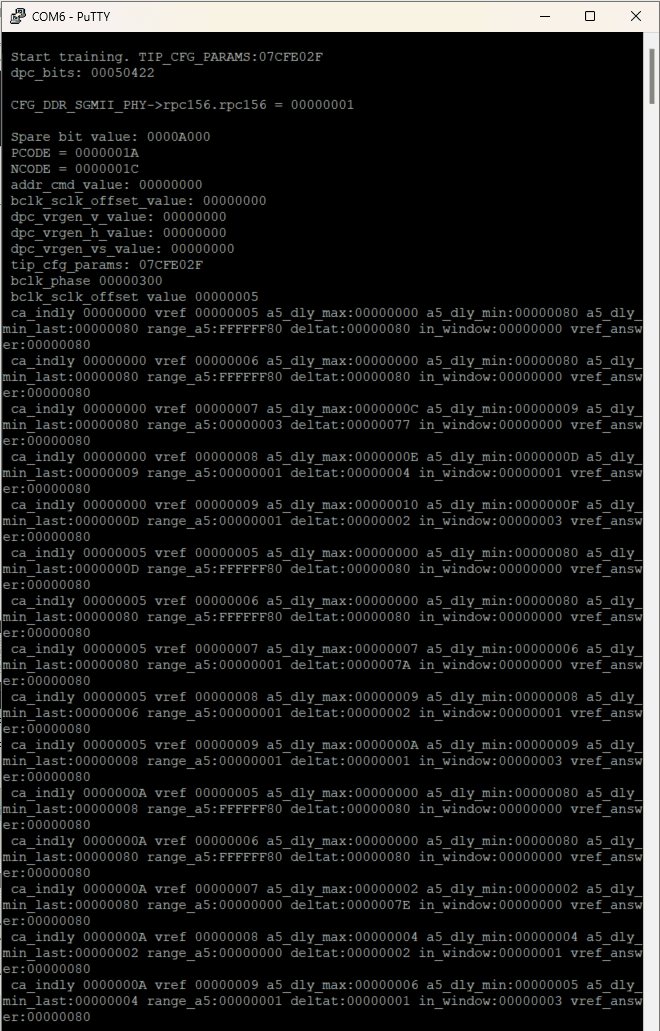

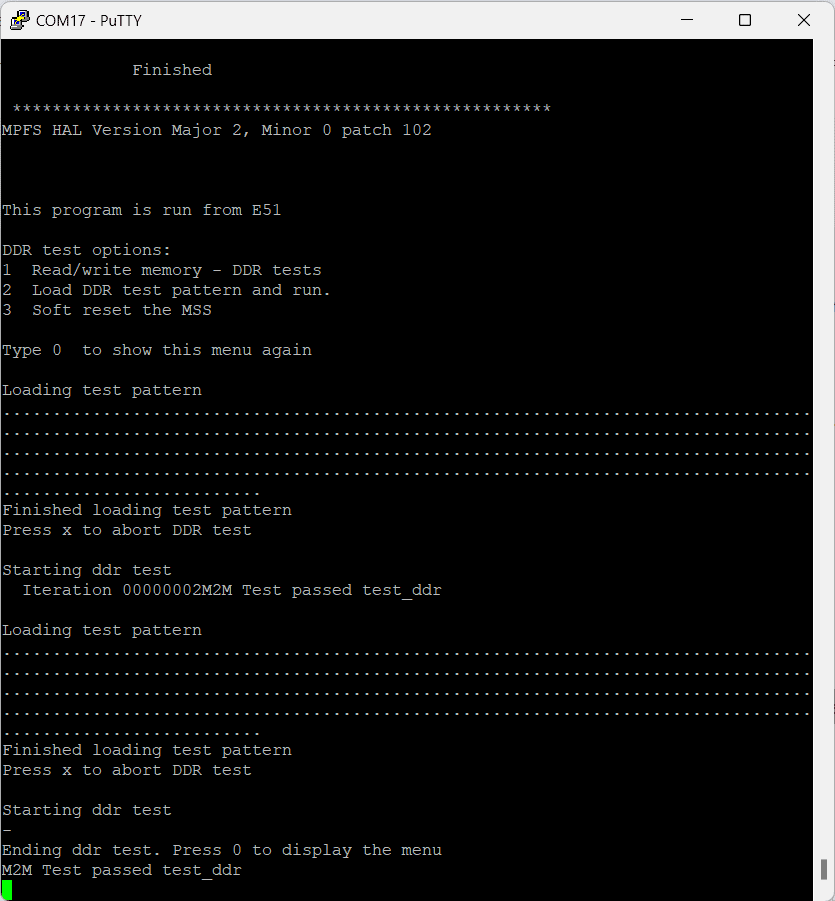

Step 25:

Once the programming is successful, launch the serial terminal and identify the correct COM port for MMUART0, which can be found in the device manager. You will observe the output printed on the serial terminal, such as Putty. A menu option will be printed to run necessary test.