So far we learned a few things about Verilog and how to create a module in Verilog and run a simulation. While simulation can tell us a lot of things about the correctness of our module, there is nothing like putting it on a piece of hardware and seeing it working. In this part of the tutorial, we will walk you through the steps for synthesizing the module and implementing it on Mimas V2 Spartan 6 FPGA Development Board (or Elbert V2 Spartan 3A FPGA Development Board) hardware.

As mentioned in part 3 of this tutorial, the test bench code is used only for simulation. To synthesize our module, we have to remove the test bench code. For those who don’t know, HDL Synthesis is the step where the HDL ( Verilog/VHDL or any other HDL for that matter) is interpreted and an equivalent hardware topology is generated. This hardware topology will be very specific to the target FPGA selected. Synthesis is a very complex process and we don’t need to know the internals to get our simple module up running.

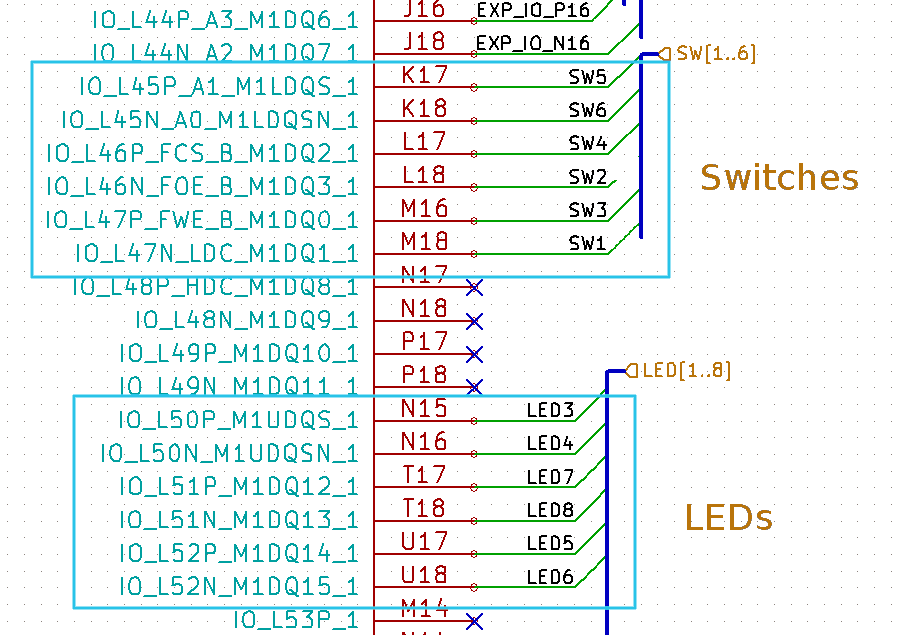

We will use Mimas V2 Spartan 6 FPGA Development Board to implement our module and the steps are very similar for Elbert V2 Spartan 3A FPGA Development Board as well. Mimas V2 board has a Xilinx Spartan 6 FPGA, a DDR SDRAM and a few other peripherals on board. The exact FPGA part number used on this board is XC6SLX9-CSG324. This is a 324 pin CSG324 BGA chip with 9K logic cells. The image below shows the part of the schematics where FPGA IOs for LEDs and Push Button Switches are connected. We will use one Push Button Switch and one LED to implement our logic.

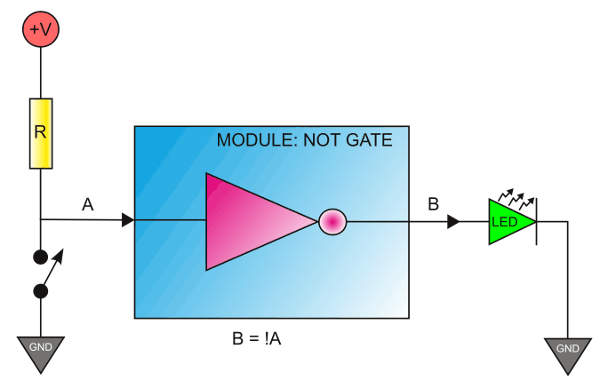

Let’s come back to our module and think about how we can implement the same on the hardware. The module in question is a NOT gate. As we know, the output of a NOT gate is always the negation of the input. We can have many possible hardware configurations to test this module. The easiest would be with a switch and a LED. See the proposed hardware configuration in the picture below.

In the above diagram, a switch is connected to an input which is pulled up to VCC using a resistor. The output is connected to a LED. Let’s take a moment to understand how this circuit is going to behave. When the switch is in open position, there will be a positive voltage ie; a logic 1 at the input (A) of the NOT gate. That means the output (B) will be at logic 0. So the LED will be in OFF condition. When the switch is closed, the input of NOT gate will become logic 0 and the output will switch to logic 1 state. And the LED will glow.

Now we know the basic hardware requirements. We need the following in our prospective hardware.

- An input capable IO with a pull-up resistor and a switch attached.

- An output capable IO with an LED attached.

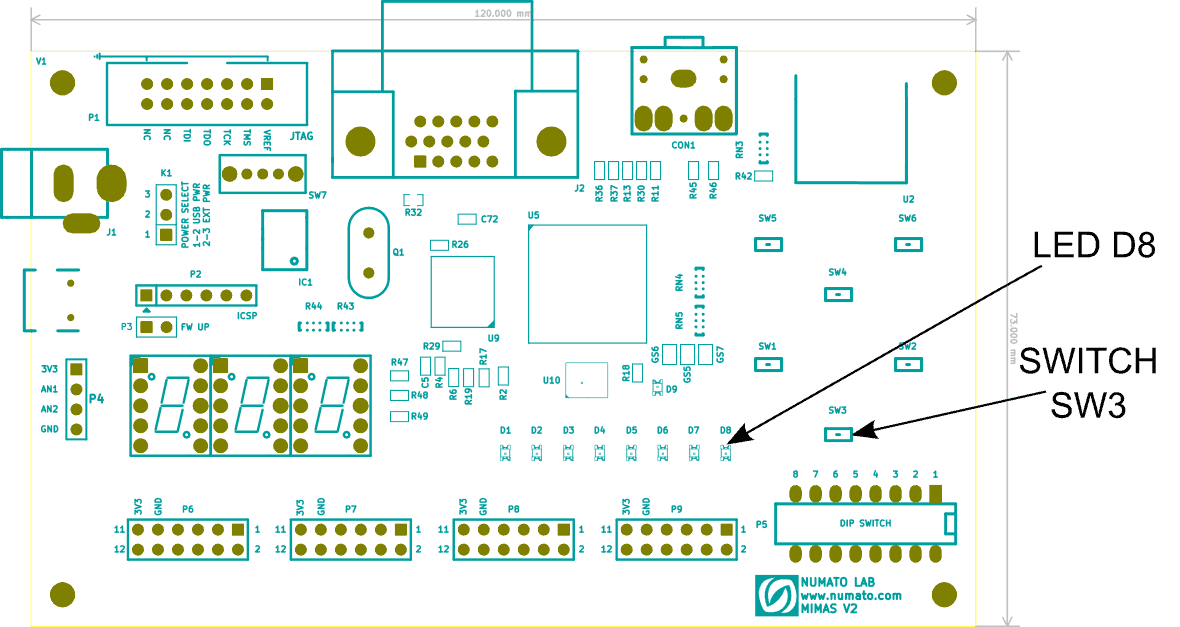

Let’s take a closer look at the Mimas V2 Spartan 6 FPGA Development Board. The following image shows the LED and switch we are planning to use on Mimas V2. Elbert V2 also has onboard switches and LEDs that can be used for this purpose. If you are using Elbert V2, LED8 and Switch SW5 would be good choices (The project attached at the tutorial for Elbert V2 uses SW5 and LED8).

As we see in the image above, Mimas V2 has six general purpose push button switches and eight LEDs for the user’s convenience. We can now take a look at the Mimas V2 schematics and learn a little bit more about where the switches and LEDs are connected. Let’s choose push button switch SW3 and LED8 for our purpose. Looking through the schematics reveals that SW3 is connected to IO M16 and LED8 is connected to T18 of the FPGA respectively (M16 and T18 are not the IO names, rather they are the names of the BGA balls that the IOs are connected to.).

We now have a Verilog module that we want to implement and we have selected a hardware platform and decided what IOs to use for implementation. Let us revisit our module. I’m reposting the module code here.

module myModule(A, B); input wire A; output wire B; assign B = !A; endmodule

Our module has two ports. Port A, which is the input and Port B, which is the output. An attentive reader would be asking now, how are we going to attach Port A to M16 of the hardware and Port B to T18 of the hardware. We will do this by defining user constraints. User constraints tell the router and the placement logic (which is a part of HDL synthesizer) on which physical pins the module signals are to be connected. We make a list of constraints and place it in a file and include that file in the project. This file is called a User Constraints File. For Xilinx tools, it is a text file with .ucf extension. Fortunately, the user constraints file for Mimas V2 is already available for download at the product page. This file has definitions for all IOs available on Mimas V2. But we don’t need all of them. So I’ll remove the unused part and post the required file contents here.

# User Constraint File for NOT gate implementation on Mimas V2

# Onboard LEDs

NET “LED” LOC = T18;

# Push Button Switches.

# Internal pull-ups need to be enabled since

# there is no pull-up resistor available on board

NET “SW” PULLUP;

NET “SW” LOC = M16;

The content of this file is pretty self-explanatory. On line No.4 it says the net LED (net is equivalent to wire/connection in the physical circuit) is connected to the physical pin T18. You might have noticed the NET “SW” PULLUP part. This means that the net SW will be pulled up to VCC. Many of the FPGA IOs have built in pull up resistors available. These resistors can be activated by appropriately mentioning it in the user constraints file. That is what exactly this particular line does. Line No. 11 connects the net SW to physical IO M16. Well, this still doesn’t answer how the ports of our module are going to be connected to the switch and LED. Like I have mentioned before, the ports of a module are equivalent to wires going in and out of the module. That, in turn, is equivalent to a net. So we can use the port names as net names in the user constraints file. So if we modify above user constraints code for our NOT gate module, it will look something like this.

# User Constraint File for NOT gate implementation on Mimas V2

# Onboard LEDs

NET “B” LOC = T18;

# Push Button Switches.

# Internal pull-ups need to be enabled since

# there is no pull-up resistor available on board

NET “A” PULLUP;

NET “A” LOC = M16;

You can download complete Xilinx ISE projects for Mimas V2 and Elbert V2 at the end of this page. The projects contain working ucf files.

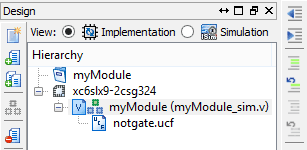

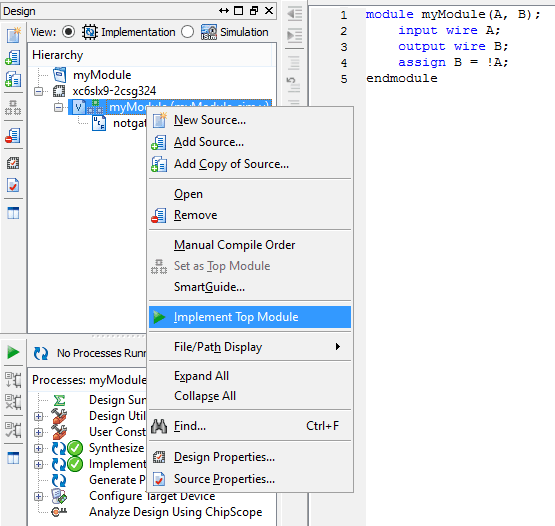

Now we have pretty much everything we need to synthesize the design and test it. Open our simulation project in Xilinx ISE Webpack and change the mode to Implementation and add the user constraints file in the project as shown in the picture below. Don’t forget to remove the test bench code from the Verilog source file and switch back to “implementation” mode in design view.

Save project and right click on the module and select “Implement Top Module” from the popup menu. Synthesis may take a few seconds to a minute. And if everything goes right you will see many green circles with a tick mark in the Process view right beneath the Hierarchy view (refer to the image below).

If any item turns yellow that means there is some kind of warning. Warnings are OK for time being. If any item turns red, there is something that went wrong. Please go back and verify all steps.

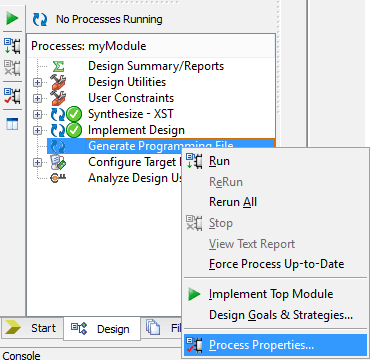

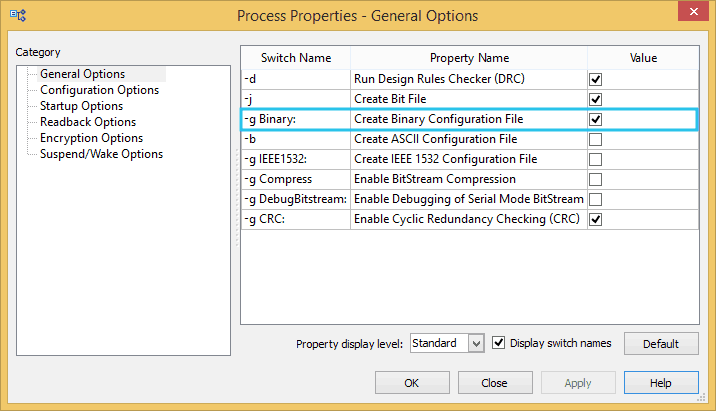

We have successfully synthesized the design. Now it is time to program the output on to the hardware. Our hardware platform Mimas V2 (and Elbert v2) requires bitstream (the final output of the synthesis process) to be in raw binary format. But ISE doesn’t generate raw binary bit file by default. We can do this by following the steps below.

- Right click on the “Generate Programming File” option in “Processes” window.

- Select “Process Properties” from the popup menu. In the dialog box, check “Create Binary Configuration File” check box and click “Apply”.

- Click “OK” to close the dialog box. Right click on “Generate Programming File” option in the process view on the left and select “Run”. Now you will be able to see a .bin file in the project directory and that file can be directly used for Mimas V2 configuration.

Now download myModule.bin (should be in the project directory if everything goes well) to Mimas V2 FPGA development board. Please see the Mimas v2 user manual to find more information about downloading output binary file to Mimas V2. Once downloading is complete, press the switch SW3 and you should see LED8 light up.

Download complete Xilinx ISE implementation project for mimas V2

Download complete Xilinx ISE implementation project for Elbert V2

Back to part 3 Continue to part 5

Would be useful to demonstrate how to add user constraint

June 8, 2017 at 3:34 amI’ve edited the code, instead of designing a circuit with a pull-up, I have simply written the rest of the two lines in the ucf.

July 6, 2017 at 8:08 pmNET “B” LOC = T18;

NET”A”LOC = M16;

Now as per my understanding the led should not glow when SW3 is pressed otherwise it should.

but when im implementing the same thing on the board the led doesn’t turn off when I press SW3.

Please help .

Read about this problem, it turns out it is not possible to define a digital circuit without a pull up or pull down. To avoid the input to float.

July 9, 2017 at 7:44 amHey , I am using mimas V2 . On headers Pin 1 and Pin 2 are GND and VCCIO. I do know that I should feed them 3.3 V DC but what supply should I use and how much current through supply is OK?

January 3, 2018 at 11:09 am# User Constraint File for AND gate implementation on Mimas V2

#Push Button Switches

NET “A” LOC = “M16″| PULLDOWN;

NET “B” LOC = “M18″| PULLDOWN;

#Onboard LEDs

NET “C” LOC = “T18″| SLEW = FAST | DRIVE = 8 ;

I wrote this ucf file for and logic implementation on spartan 6. A,B are my inputs and C is my output. This does not seem to work what so ever i modify. please help.

August 9, 2018 at 1:52 pmFor those that run into the same issue I had to set the module speed to -3 vice -2 to get this demo working.

August 20, 2019 at 6:42 pm