Introduction:

HDMI (High-Definition Multimedia Interface) is a widely used audio/video interface for transmitting uncompressed video and digital audio data between compatible devices with high fidelity. It serves as the digital replacement for analog video standards, enabling seamless connections between devices such as display controllers, computer monitors, video projectors, digital televisions, and audio devices. HDMI achieves this by utilizing TMDS (Transition Minimized Differential Signaling) for data transmission, ensuring minimized bit transitions and robust signal integrity. The pixel data is transmitted serially at a rate ten times the pixel clock frequency, enabling high-resolution video output and precise synchronization.

In this project, we demonstrate HDMI functionality using the Zynq-7000 Programmable Logic (PL) section. The Zynq PL enables a flexible and high-performance implementation of the HDMI protocol, leveraging its FPGA fabric to handle video data processing and signal transmission. Although this project uses HDMI for output, the core implementation principles also align with DVI-D (Digital Visual Interface-Digital), as both interfaces share the same signal structure. Consequently, HDMI-compatible monitors seamlessly support DVI-D signals transmitted over HDMI cables.

This project focuses on the generation and transmission of HDMI video signals from the Zynq PL section, validating the output on an external monitor. It highlights the versatility of Zynq’s FPGA capabilities for handling complex multimedia protocols, making it an ideal platform for advanced video and audio processing applications.

Prerequisites:

Hardware:

- TityraCore D200 SODIMM Module.

- TityraCore SoC carrier.

- HDMI cable and a compatible monitor.

- Xilinx Platform Cable II JTAG debugger.

- USB Type C Cable.

- 5V-12V DC Power Supply.

Software:

- Xilinx Vivado Design Suite 2024.1

Let’s get started

The following steps will walk you through the process of creating the HDMI output project on TityraCore D200 using Xilinx Vivado Design Suite.

Step 1:

Download and install Vivado Board Support Package files for TityraCore D200 from here. Follow the readme in the link on how to install Vivado Board Support Package files for Numato Lab’s boards.

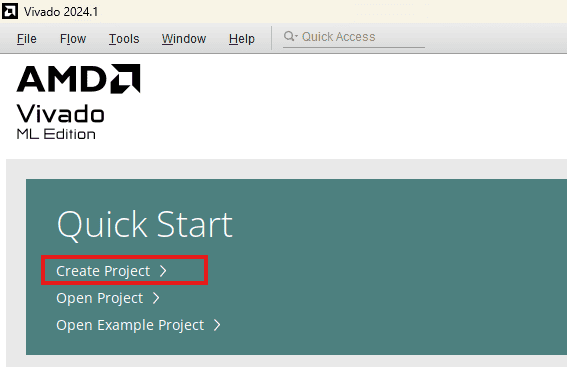

Step 2:

Start Vivado Design Suite, and select “Create New Project” from Quick Start section. The project wizard will pop up. Press next to proceed with creating the project.

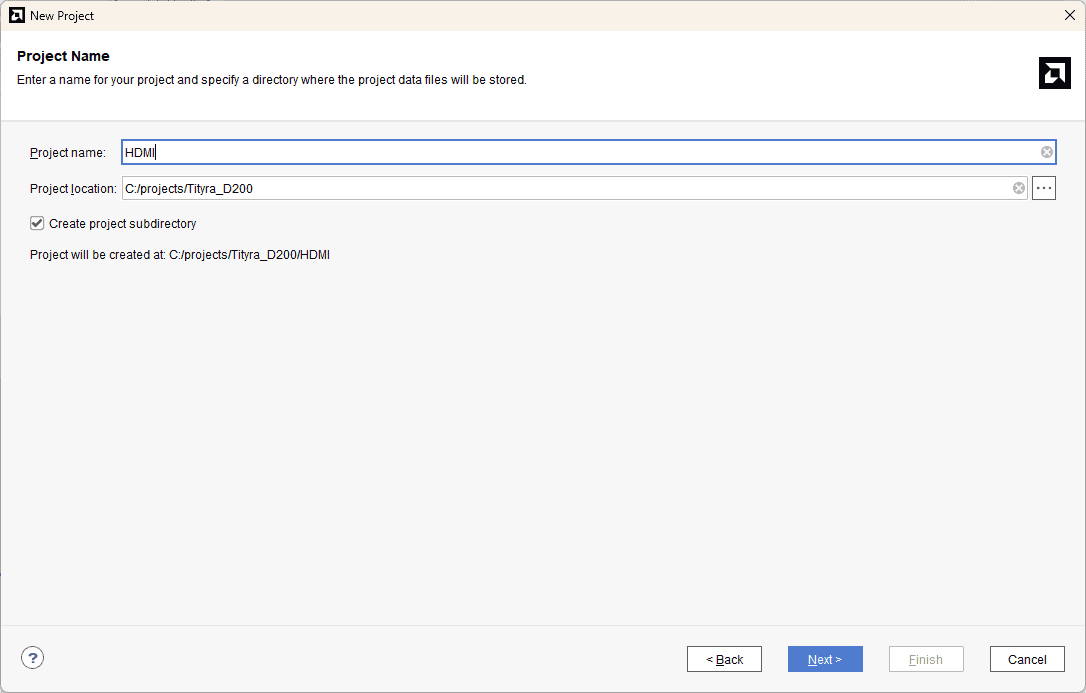

Step 3:

Type in a project name and save it at a convenient location. For this example “HDMI” is used as project name, but feel free to use any name. Select the check box below to keep all project files in a single folder. The image below shows the settings for the example project. Click “Next” to continue.

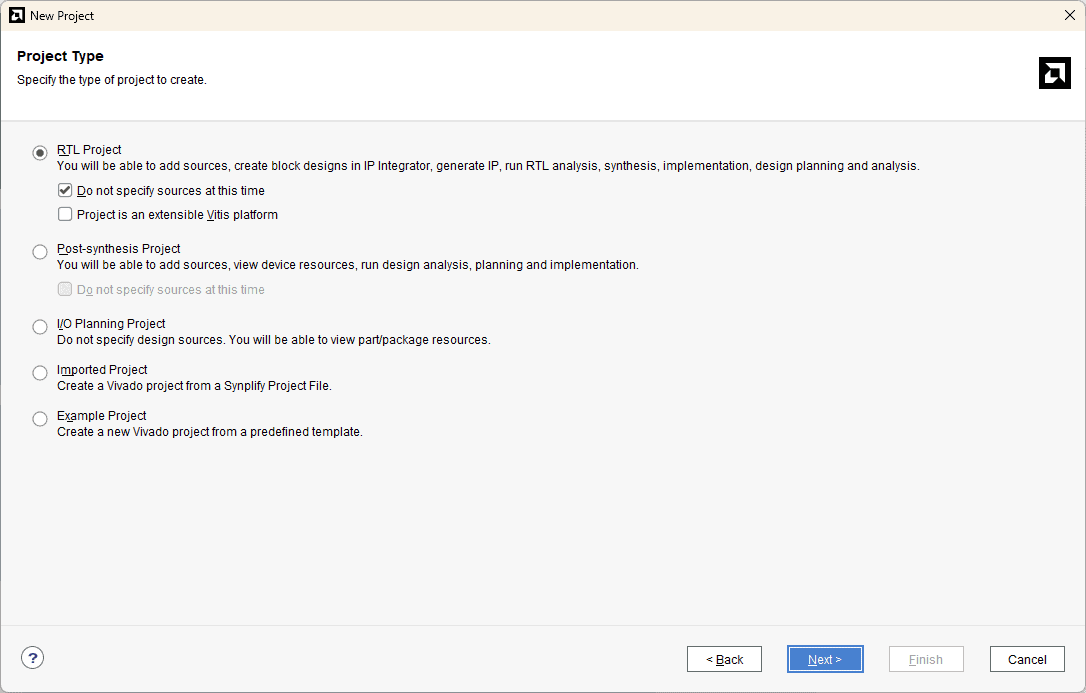

Step 4:

Choose “RTL Project” as project type and check the option “Do not specify sources at this time”.

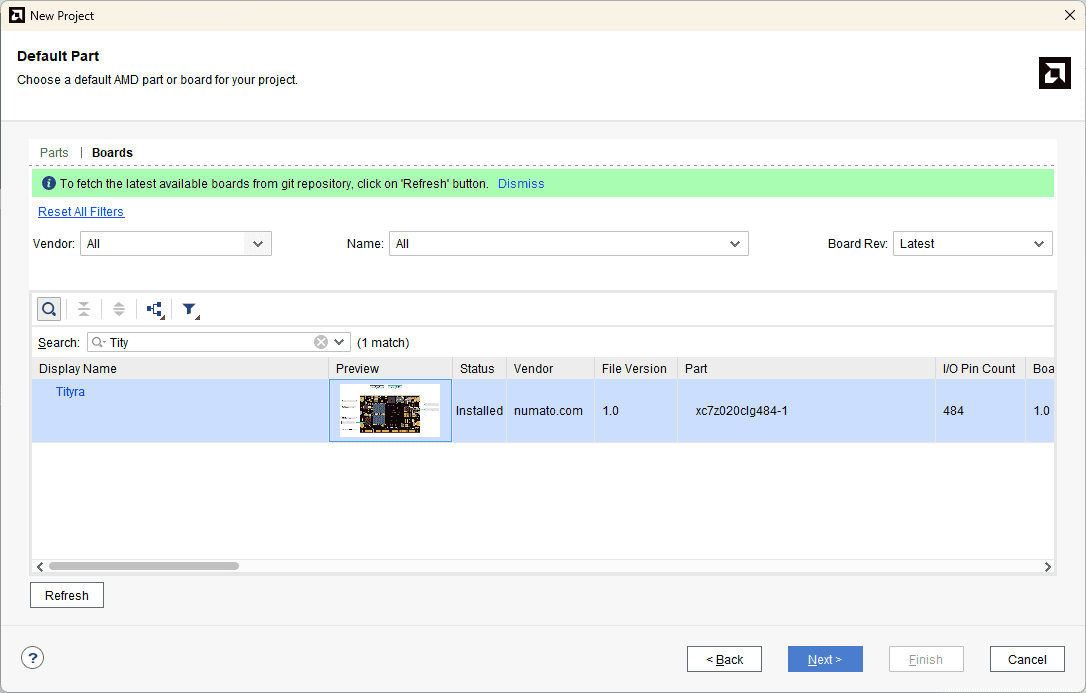

Step 5:

At the “Default Part” step, select “Boards” and choose Vendor as “numato.com”. Select “Tityra” and click “Next”. If Tityra is not displayed in the boards list, you will need to install Tityra board support files correctly.

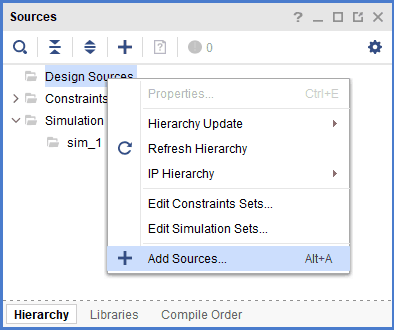

Step 6:

In the “Sources” tab, right-click on the “Design Sources” and select “Add Sources”. It will open a new “Add Sources” window.

Step 7:

Download and extract the RTL source files from here. Add the RTL source file by selecting “Add Files”

The HDMI interface has three pairs of differential data signals each one pair is for each color i.e Red, Blue and Green and one pair of differential clock signals:

data_p[2:0] & data_n[2:0]: These differential signals in HDMI interface carry the audio/video data to display on the screen.

clk_p & clk_n: These are the pixel clock differential signal of HDMI interface.

First, VGA signals are generated inside “vga” module. Then the VGA signals are encoded to 10-bits per channel and the data is then serialized to 10x of pixel clock rate. Finally, the three channels along with pixel clock are driven out using TMDS differential drivers.

The source file has top module (dvid_test) in which two sub modules are instantiated (dvid & vga). This module also include the Clocking IP core to generate required clocks for VGA and DVI-D.

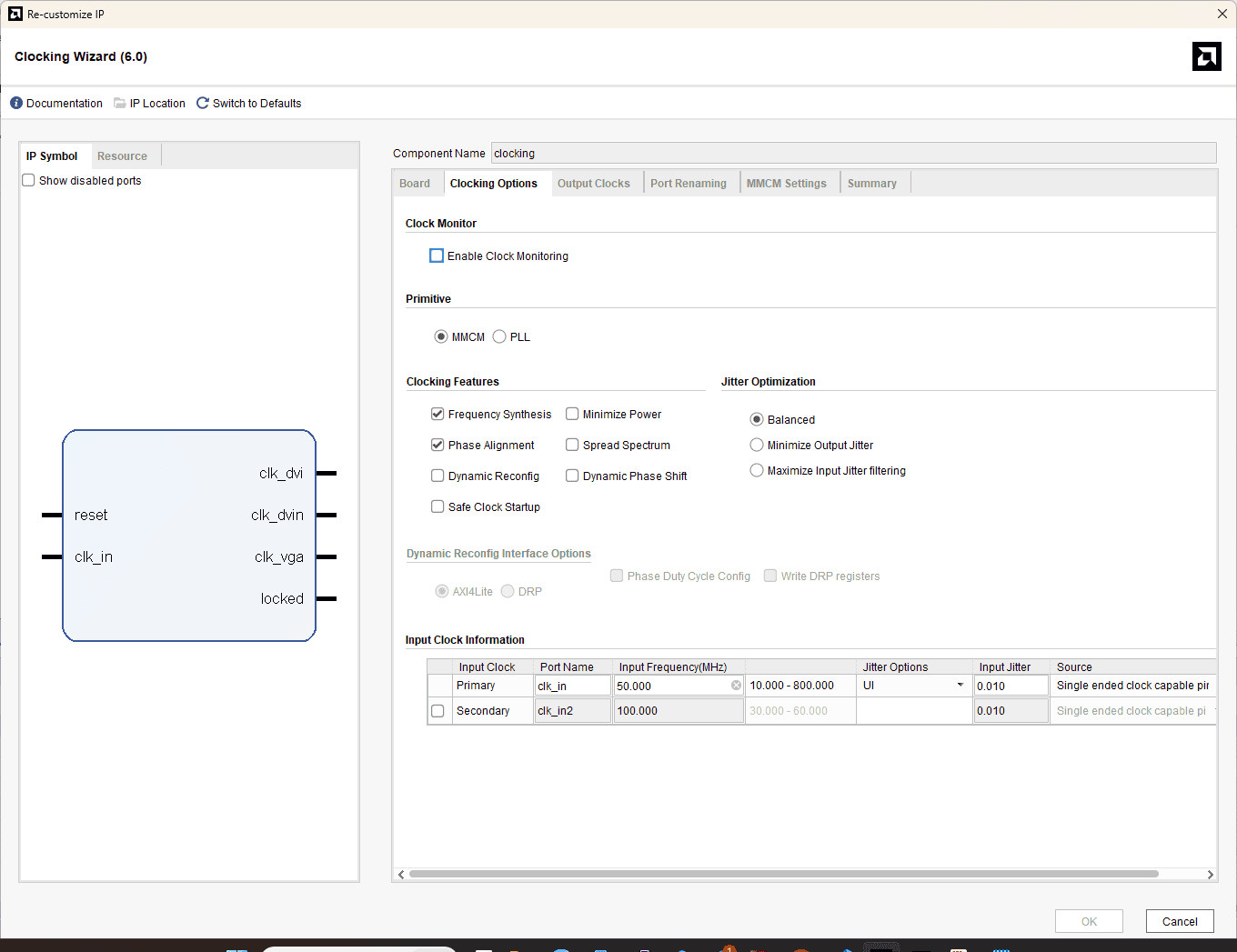

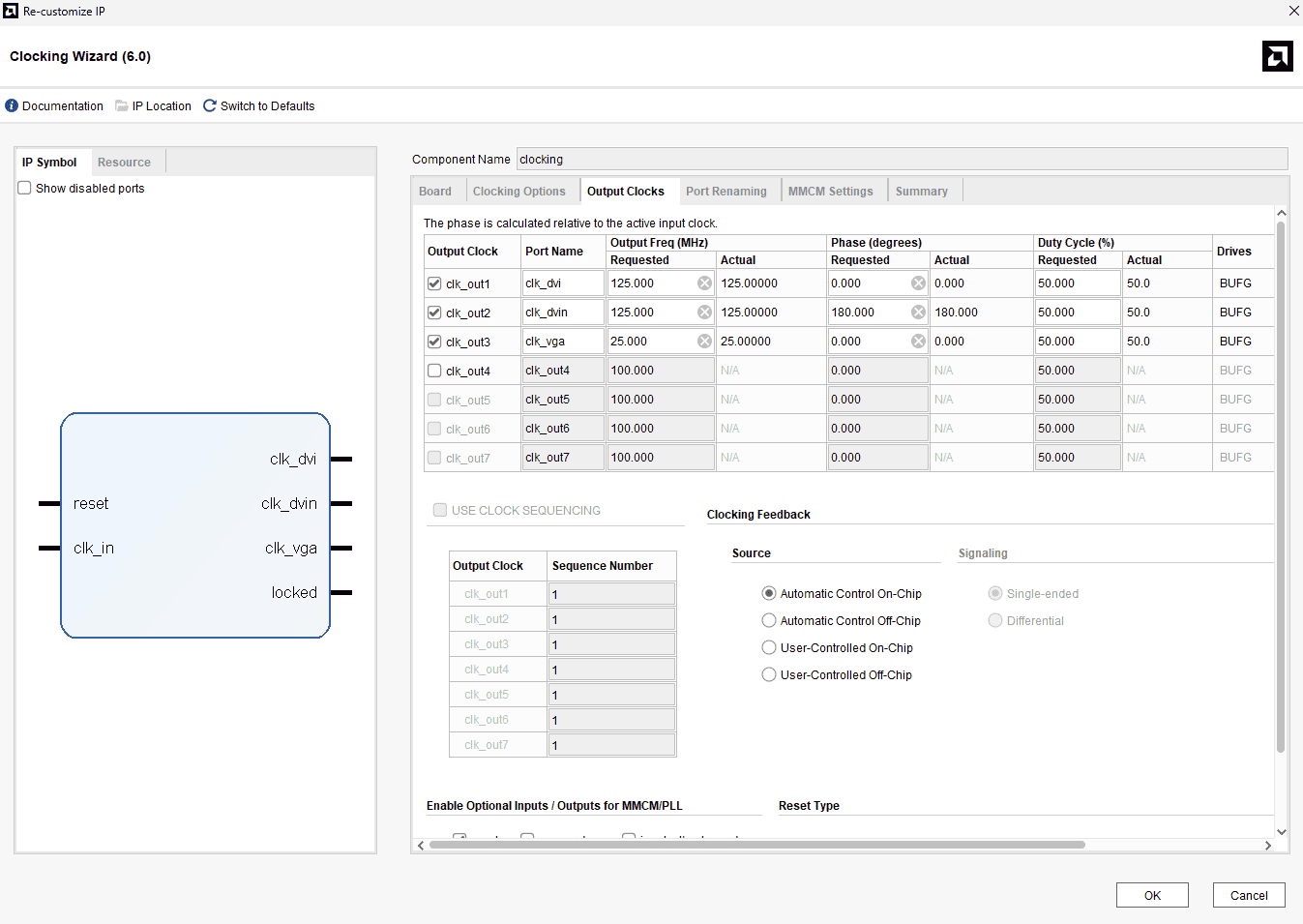

clocking : This module generates required clocks for VGA and DVI-D. The 100MHz clock from the on board oscillator is an input and this input clock drive the other three clocks from it.In this module clk_in (100MHz) is the input clock and the clk_dvi (125MHz), clk_dvin (125MHz), clk_vga (25MHz) are the output clocks for VGA and DVI-D. clk_dvin is 180 degrees out of phase to clk_dvi. These clocks are used for serialization using ODDR2. This module is also having Active High reset signal.

vga: VGA signals are generated in this module with 640×480@60Hz resolution at 25 MHz pixel clock frequency.

dvid: The signals generated from the clocking module and vga module are given as input to dvid module and the DVI-D TMDS signals are generated as the output. It uses TMDS_encoder module to generate TMDS signals. TMDS uses 8b/10b encoding in which the 8-bit color data (red, green & blue) generated in VGA module and is converted to 10 bits. Then this data is serialized using ODDR2 (Double Data Rate primitive). The 10-bit TMDS data is generated at 25 MHz. ODDR2 uses 5 times the frequency of pixel clock (i.e. 125MHz) to serialize the 10-bit encoded data. Note that ODDR2 serializes 2-bits in 1 clock cycle of 125MHz clock. This serialized data is converted into differential signals in the top module (dvid_test) using OBUFDS drivers.

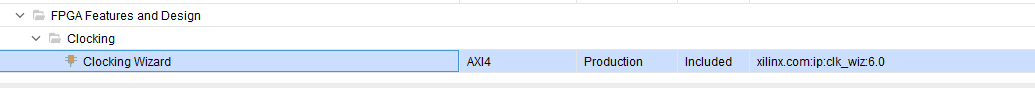

Step 8:

In the “Flow Navigator” panel, click “IP Catalog” under the “PROJECT MANAGER” section. In the IP Catalog, search for “Clocking Wizard” IP and double click on it. The “Customize IP” window will open.

Step 9:

In “Clocking Options” tab, give Component Name as “clocking” and primary clock port name as “clk_in” and set the input Frequency of “clk_in” as “50MHz” .

In “Output Clocks” tab, enable 3 output clocks and provide their name, frequency as well as phase as shown below. Click “OK”.

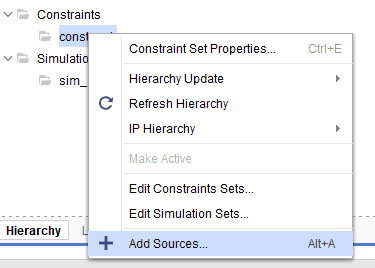

Step 10:

Go to “Add Sources” under the Flow Navigator -> PROJECT MANAGER window, select the “Add or create constraints” and click “Next”. Click on “Create file” and give a name for the XDC and select “File type” as “XDC”. Click “OK” and “Finish”.

Step 11:

Copy the following constraints to the newly created constraints file:

##Clock Signal

set_property -dict {PACKAGE_PIN W17 IOSTANDARD LVCMOS33} [get_ports clk_in]

set_property -dict {PACKAGE_PIN M16 IOSTANDARD LVCMOS33} [get_ports reset]

###HDMI out

set_property -dict {PACKAGE_PIN U17 IOSTANDARD TMDS_33} [get_ports {data_p[0]}]

set_property -dict {PACKAGE_PIN V17 IOSTANDARD TMDS_33} [get_ports {data_n[0]}]

set_property -dict {PACKAGE_PIN AA17 IOSTANDARD TMDS_33} [get_ports {data_p[1]}]

set_property -dict {PACKAGE_PIN AB17 IOSTANDARD TMDS_33} [get_ports {data_n[1]}]

set_property -dict {PACKAGE_PIN AA16 IOSTANDARD TMDS_33} [get_ports {data_p[2]}]

set_property -dict {PACKAGE_PIN AB16 IOSTANDARD TMDS_33} [get_ports {data_n[2]}]

set_property -dict {PACKAGE_PIN V14 IOSTANDARD TMDS_33} [get_ports clk_p]

set_property -dict {PACKAGE_PIN V15 IOSTANDARD TMDS_33} [get_ports clk_n]

Step 12:

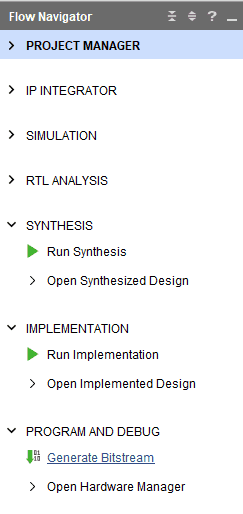

In Flow Navigator panel, click “Generate Bitstream” to synthesize, implement and to generate bitstream.

Step 13:

Set up the hardware for testing the design. Connect an HDMI cable from the HDMI_OUT port on the TityraCore D200 carrier board to a monitor, and then power on the carrier board.

Step 14:

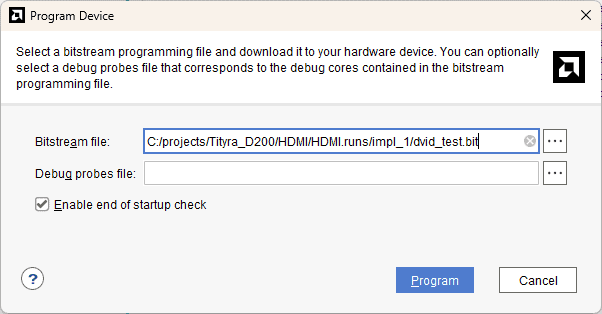

To program the TityraCore D200 with the generated bitstream, follow the steps mentioned below:

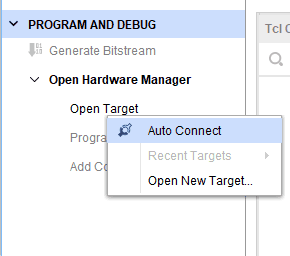

- Once the Bitstream is generated successfully, expand the “Open Hardware Manager” under “PROGRAM AND DEBUG” section of Flow Navigator panel.

- Then click “Open Target->Auto Connect”.

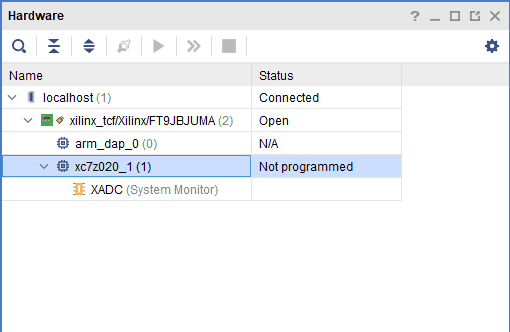

You can now see that the board is detected.

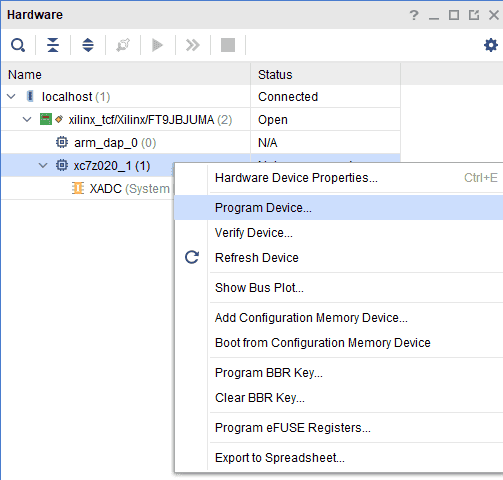

Now, right click on the device “xc7z020_1(1)”and click “Program Device”.

Select the TityraCore HDMI out bitstream and click “Program”.

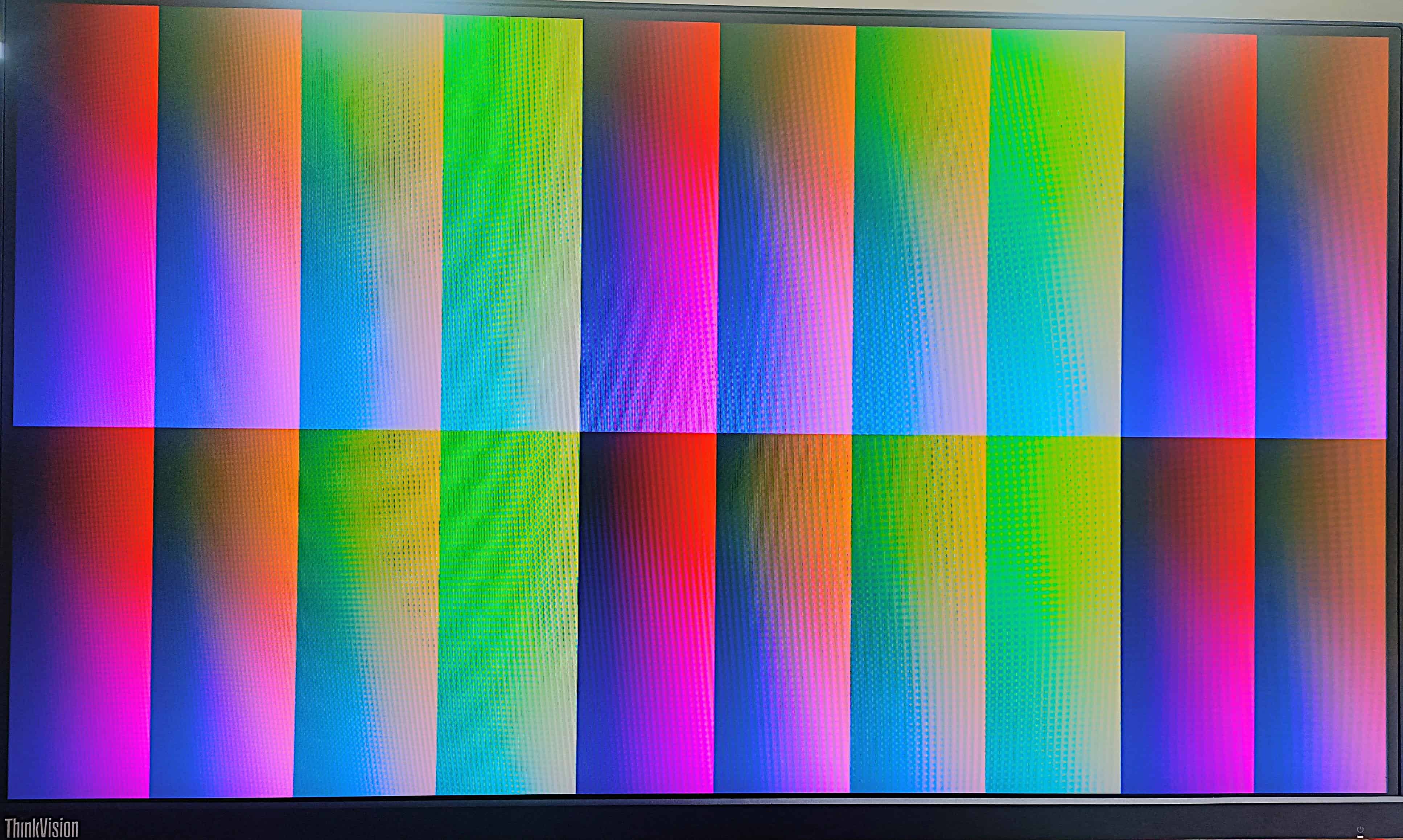

Once TityraCore D200 is successfully programmed, you will be observing with the color pattern at 640×480@60Hz resolution as shown in the following image.

That was it! You can generate different output pattern for differentvgamodule and also with higher resolution. Congratulations!