Introduction

AMD Vivado Design Suite is used for the synthesis, implementation, and analysis of HDL designs, and also provides a complete environment for Zynq UltraScale+ MPSoC development. Vivado is the recommended design tool for creating new projects targeting UltraScale/UltraScale+ devices, as well as other AMD FPGA families. In this guide, we will use Vivado to build a simple “Hello World” application for the EagleCore ZU MPSoC SOM, running on the ARM processing system (PS).

Prerequisites

To follow this article, you would need the following:

- Hardware:

- EagleCore ZU-Plus MPSoC SOM.

- EagleCore ZU01 Carrier.

- AMD Platform Cable II JTAG debugger.

- USB Type C Cable.

- 12V DC Power Supply.

- Software:

- AMD Vivado Design Suite 2025.1

- Vitis 2025.2

Let’s get started

The following steps will walk you through the process of creating a new project with Vivado and building a hardware platform with Zynq Ultrascale+ processing system using IP integrator. This article is written for Numato Lab’s Eaglecore ZU-plus MPSoC SOM, but can be adapted to any other Zynq based platform with minor changes. Screenshots are added wherever possible to make the process easier to the reader.

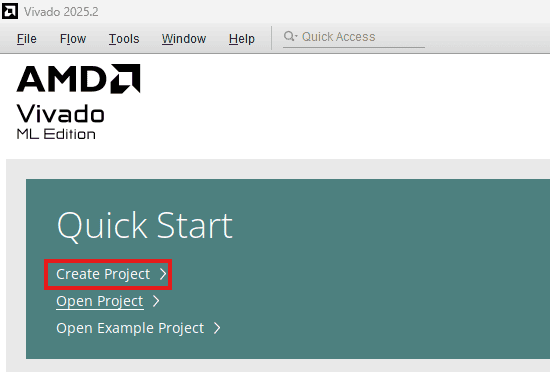

Step 1:

Start Vivado Design Suite, and select “Create New Project” from Quick Start section. The project wizard will pop up. Press next to proceed with creating the project.

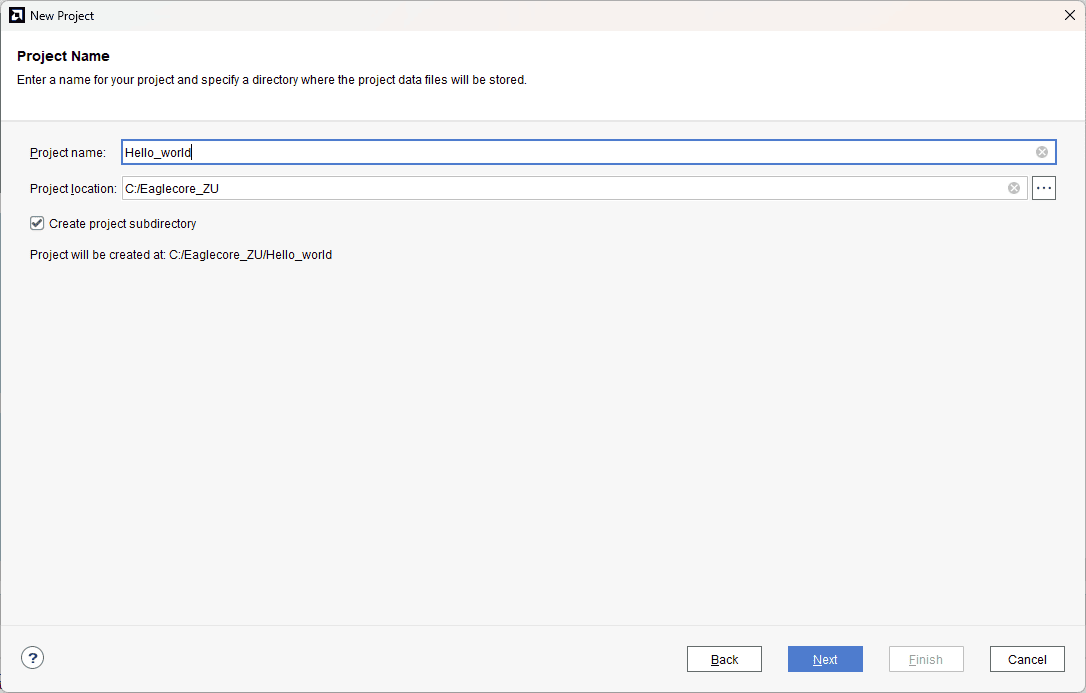

Step 2:

Type in a project name and save it at a convenient location. For this example “Hello_world” is used as project name, but feel free to use any name. Select the check box below to keep all project files in a single folder. The image below shows the settings for the example project. Click “Next” to continue.

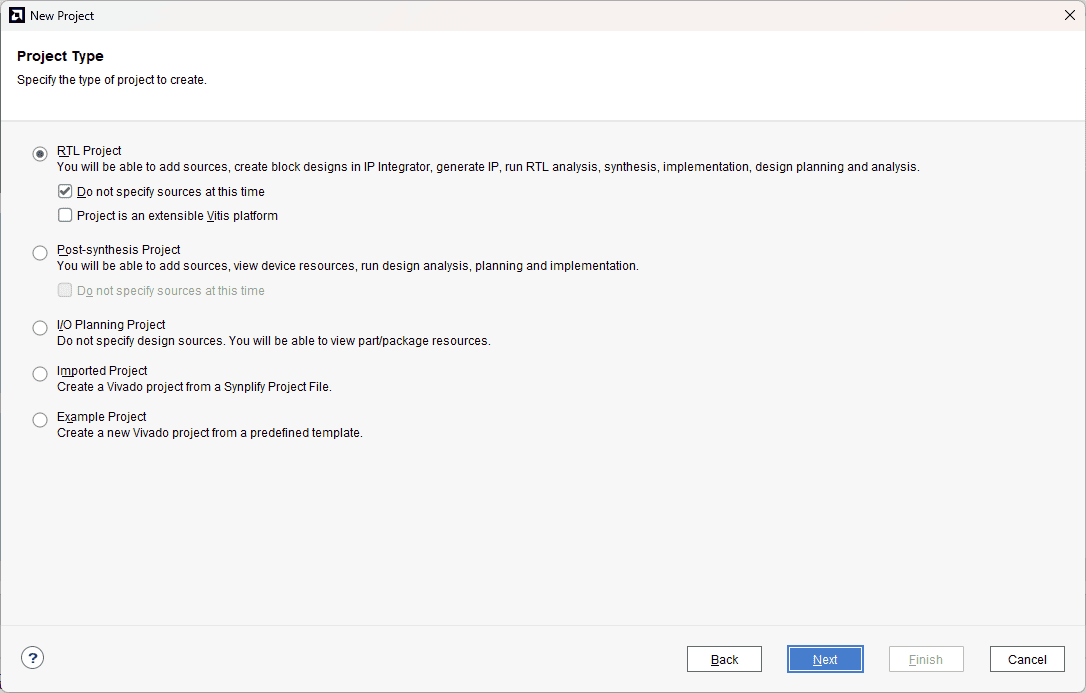

Step 3:

Choose “RTL Project” as project type and check the option “Do not specify sources at this time”.

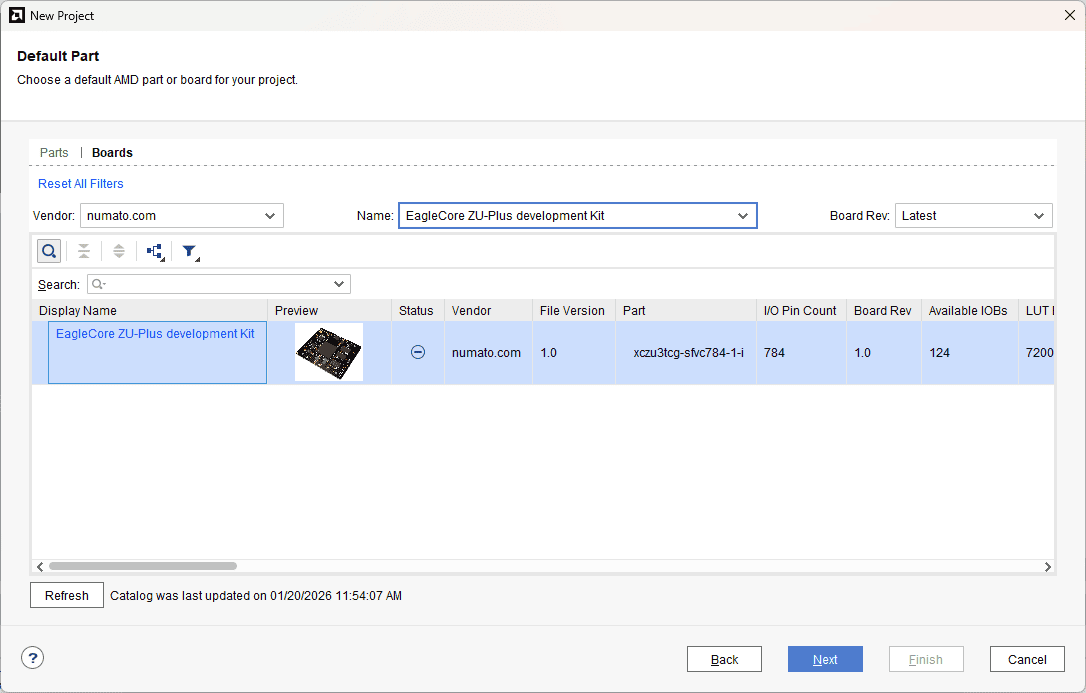

Step 4:

At the “Default Part” stage, switch to the “Boards” tab and set the vendor to numato.com. Select “EagleCore Zu-plus development kit” and click Next. If the EagleCore Zu-plus development kit board does not appear in the list, click “Refresh” to update the board catalog. Vivado will then download the latest board files, after which EagleCore ZU-plus will become available for selection.

Continue the wizard and finish creating the project. When the new project wizard exits, a new project will be opened up in Vivado with the settings you have selected.

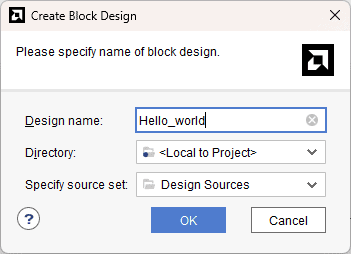

Step 5:

Under Flow Navigator, select “Create Block Design” in IP Integrator. Give an appropriate name to design. We will call it “Hello_world” for example.

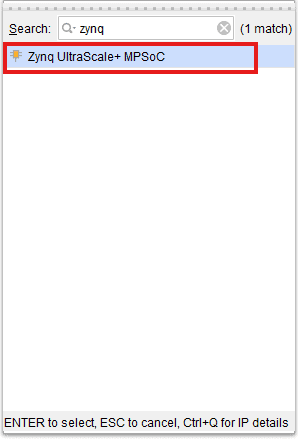

Step 6:

Go to Diagram window, right click and select “Add IP” from the popup menu. Search for Zynq Ultrascale+ MPSoC. Add it to block design by double clicking.

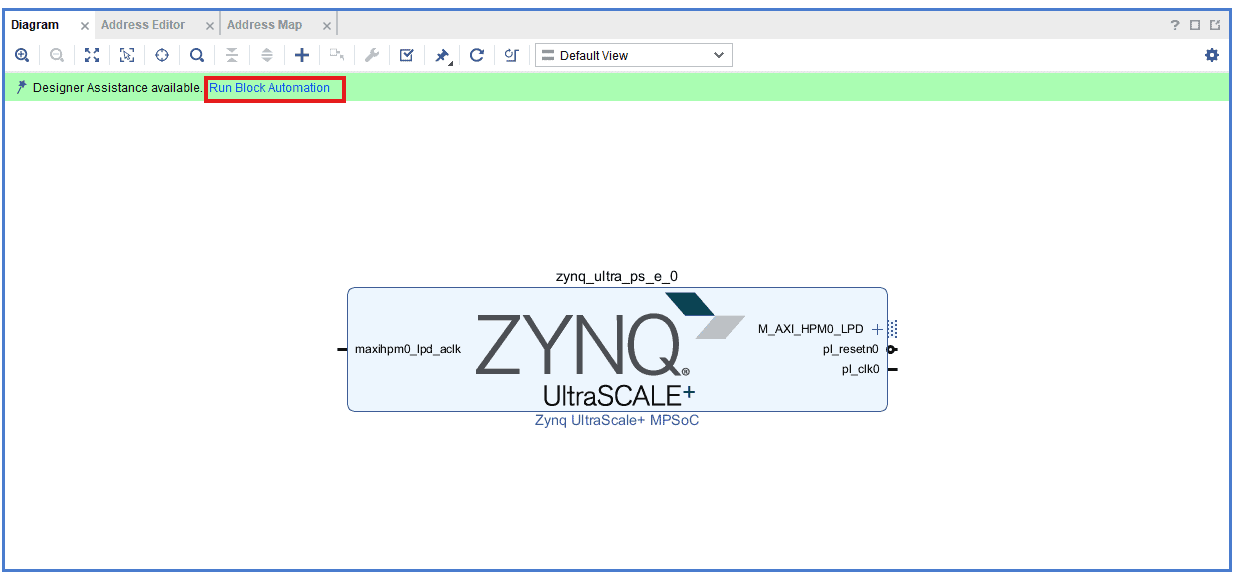

Step 7:

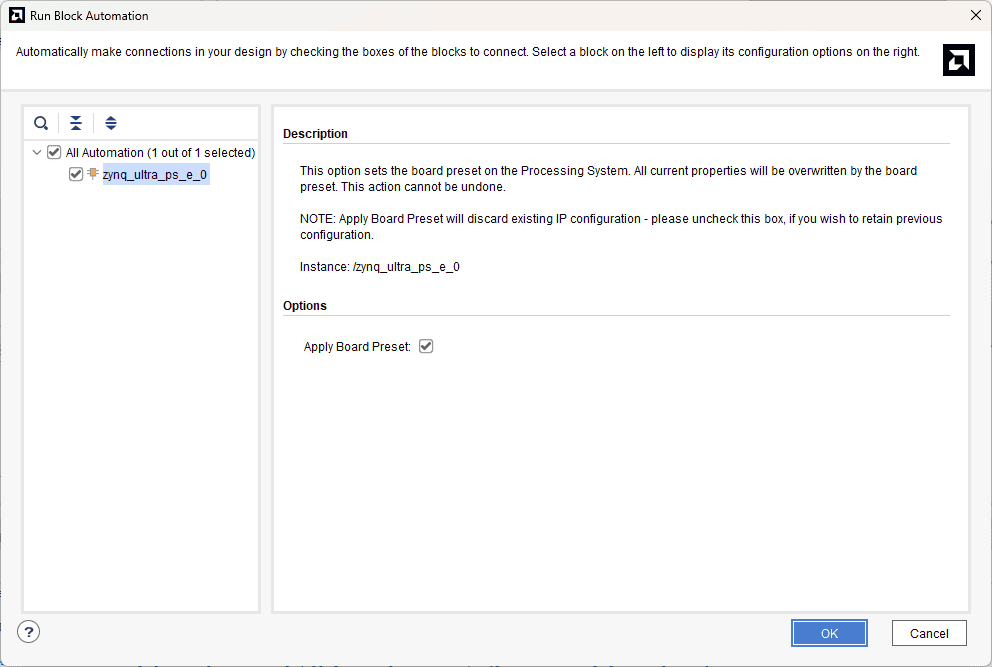

Click on “Run Block Automation” option on the green bar.

Step 8:

In the “Run Block Automation” window, select the options as in image below and click OK.

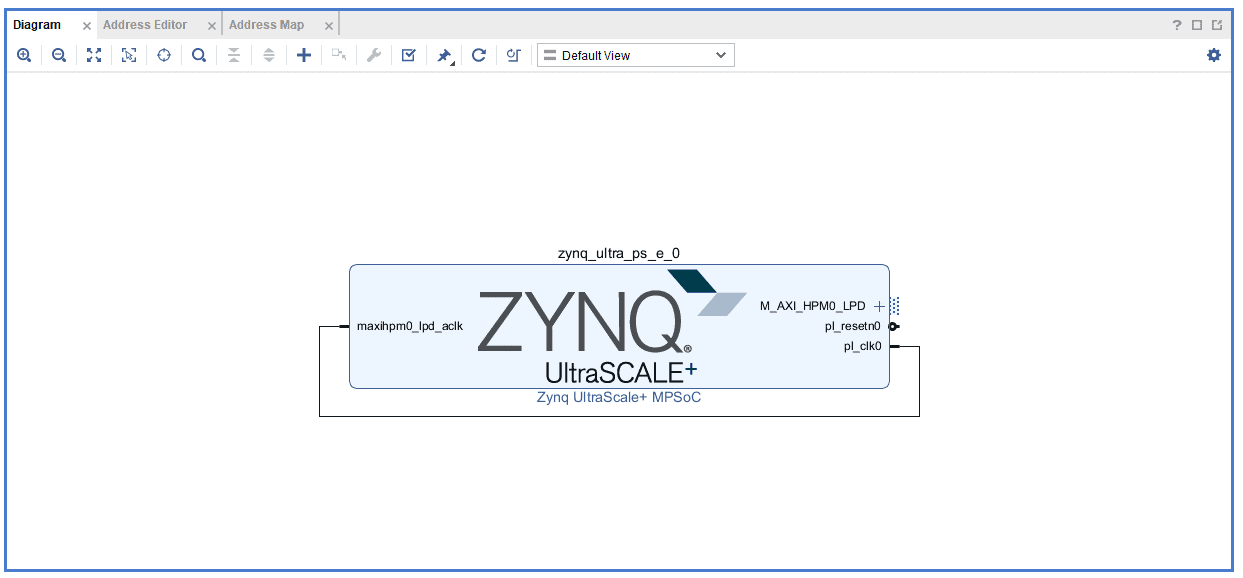

After running Block Automation, verify and complete the connections as shown in the image below.

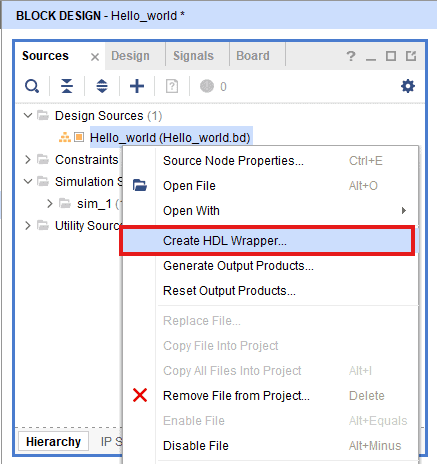

Step 9:

Go to “Sources” tab, right click on “Hello_world” design file and select “Create HDL Wrapper”. Click OK on the window that appears to finish generating wrapper

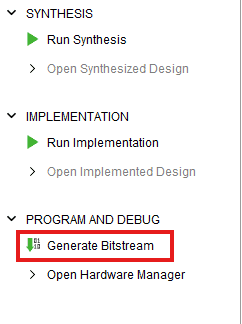

Step 10:

Click “Generate Bitstream” under PROGRAM AND DEBUG section and click “Yes” in any subsequent dialog window which comes up.

Step 11:

Once the bitstream is successfully generated, close any “Bitstream Generation Completed” dialog which comes up asking for what to do next , click OK.

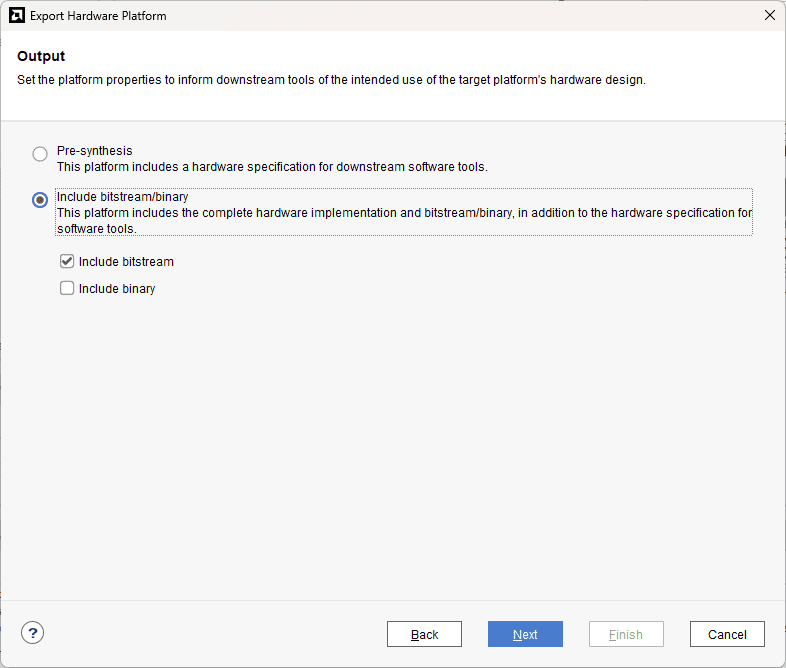

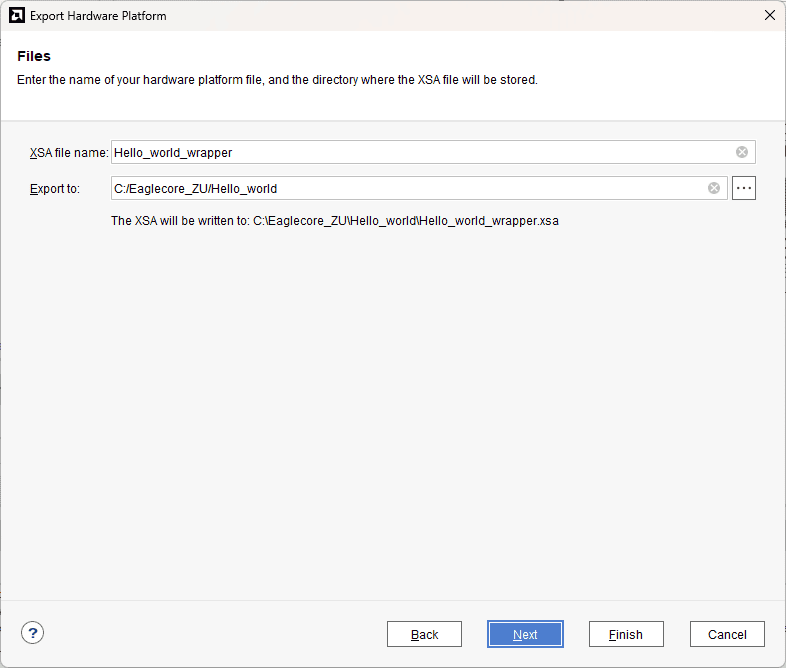

Go to File -> Export -> Export Hardware…

Check “Include bitstream”, keep “Export to:” default, and click OK.

Step 12:

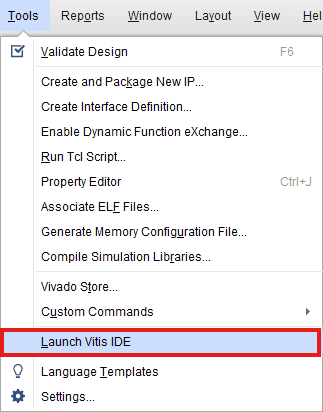

Select Launch Vitis IDE from the Tools menu.

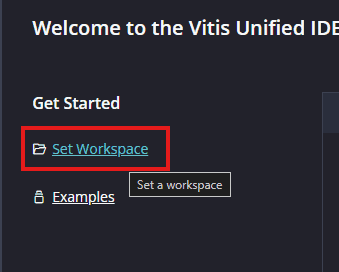

Step 13:

After Vitis Unified IDE window opens, click on “Set Workspace” and select necessary folder to keep the Vitis files.

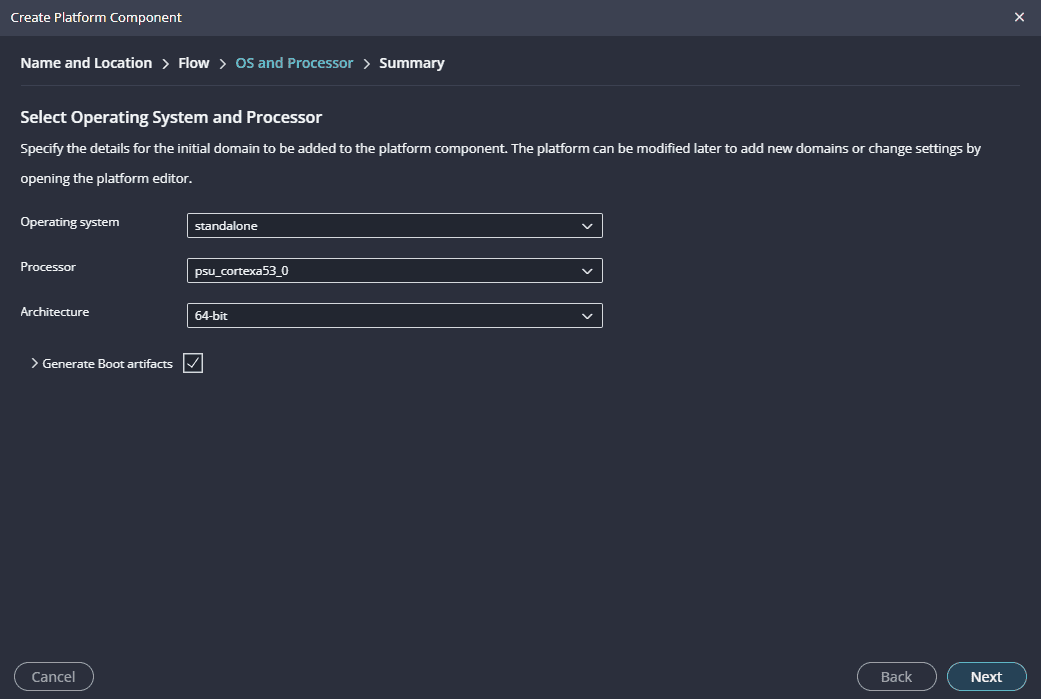

Step 14:

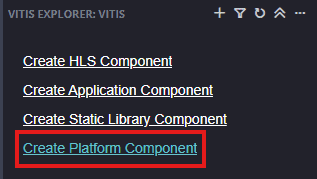

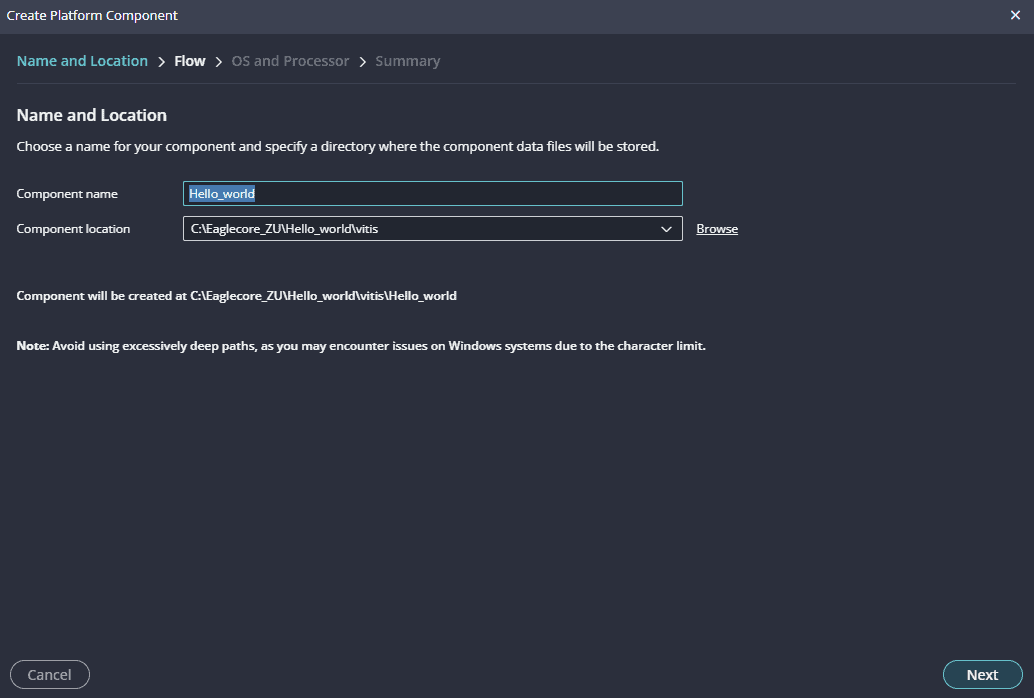

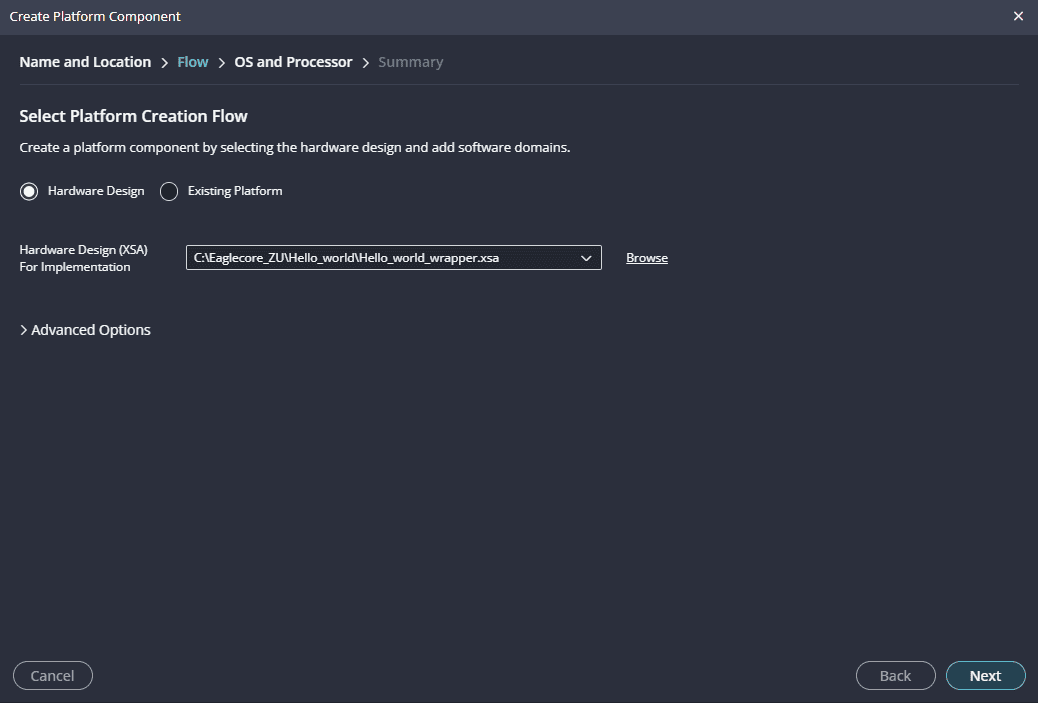

Create a new platform for the project, by selecting “Create Platform Component”, click “Next”, in the Flow tab select the XSA file saved using the step 11 and finally click “Next” and “Finish” respectively.

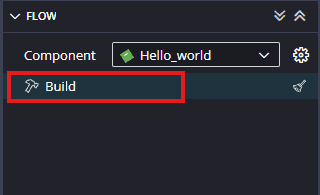

After successful creation of the platform, build the platform.

Step 15:

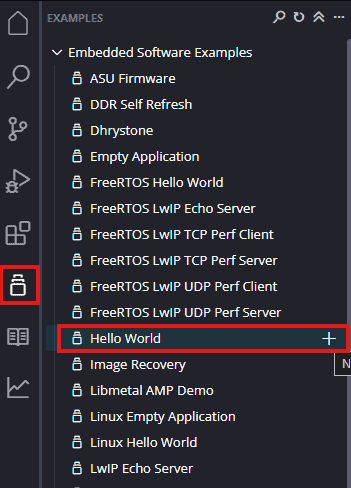

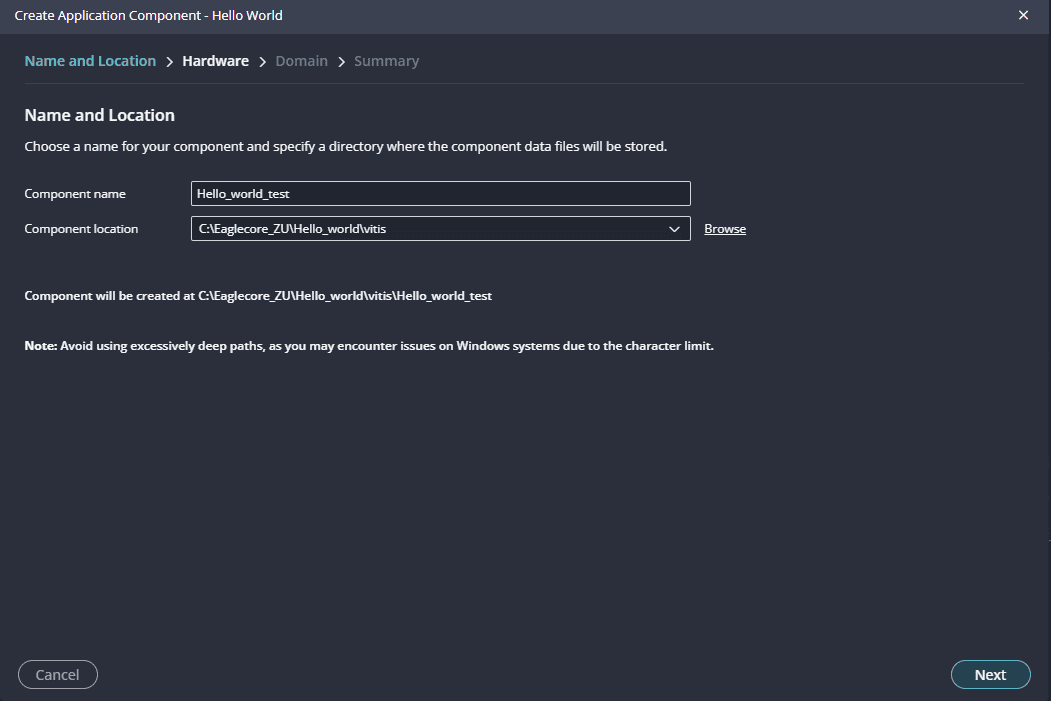

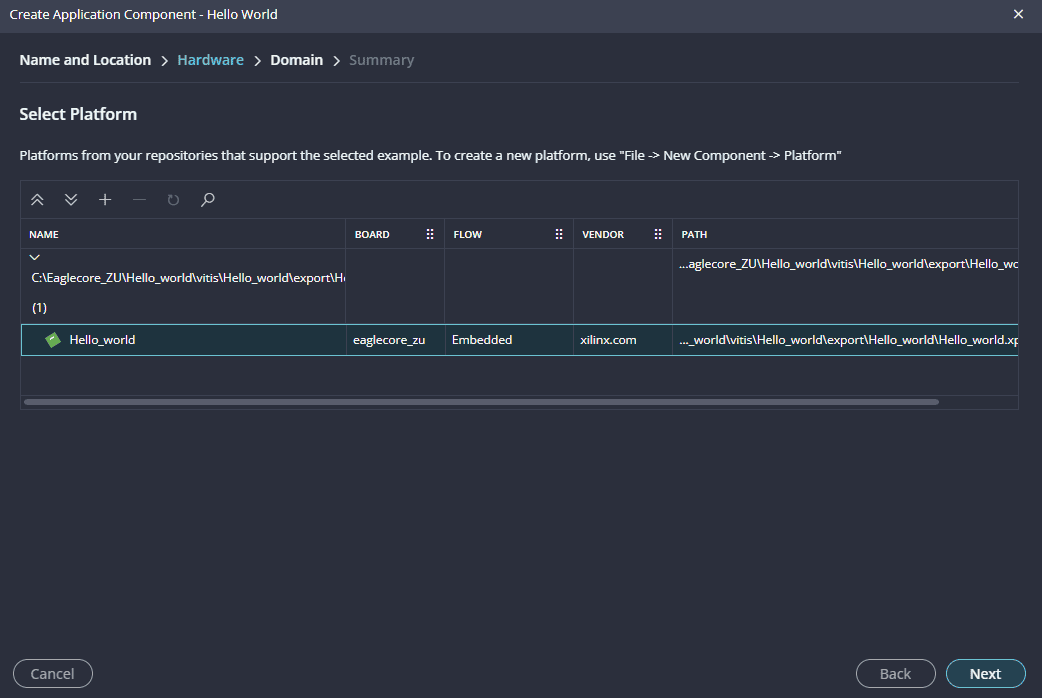

Next create the Hello_world_test Application component by selecting the “Hello world” template from the “examples”,

In “Create Application Component” tab specify project name and location, click “Next”

Select newly created Platform and click “Next”.

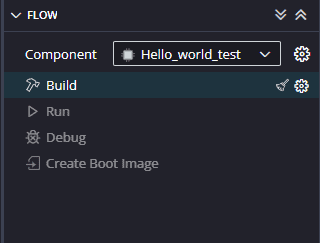

When the Hello world project is added successfully, build the project manually.

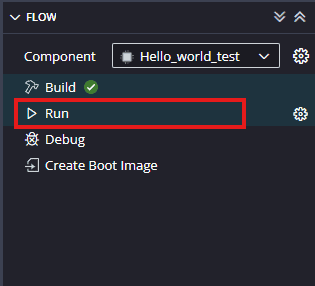

Step 16:

Once the build is completed sucessfully, power up the EagleCore ZU module using an external 12V DC power supply. Then, connect a Type-C cable to program the board (Note: ensure that PGM SELis set to USB programming).

Step 17:

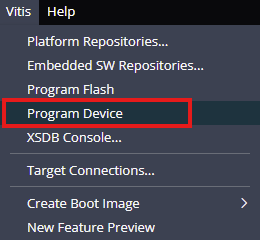

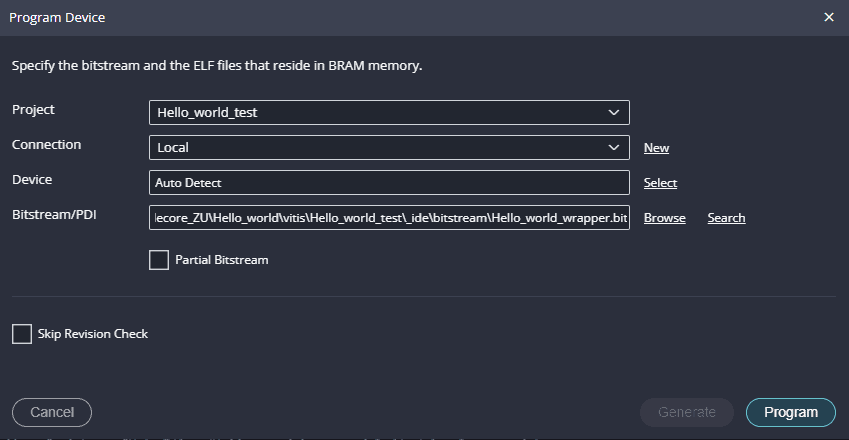

Program the FPGA on EagleCore ZU with a simple boot loop program by selecting the Program Device option from the Vitis menu.

Once the “Program Device” window opens click on “Program“.

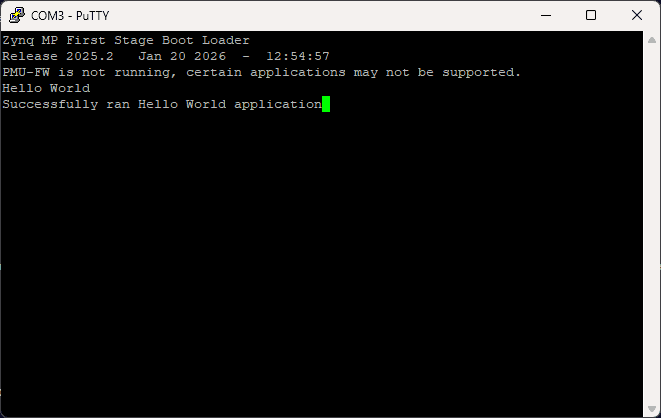

Step 18:

Meanwhile, open any serial terminal program (such as PuTTY, Teraterm etc) and open the port corresponding to Eaglecore ZU with a 115200baud rate. Program the board by selecting the “Run”.

Step 19:

If everything went well, the application running on the board should print “Hello World” over the UART and should be displayed on the Serial Terminal application.