Introduction

Testing DDR4 memory for Neutron KU60 FPGA Development board involves using specialized tools to ensure the memory functions correctly within the FPGA environment. In Vitis, a software development platform by AMD, a memory test template can be utilized to perform these tests. This template helps in validating the performance and reliability of DDR4 memory by running predefined test patterns and checking for errors. The Purpose of this article is to help readers to understand how to test DDR4 memory available on Neutron KU60 FPGA Board using Memory tests template.

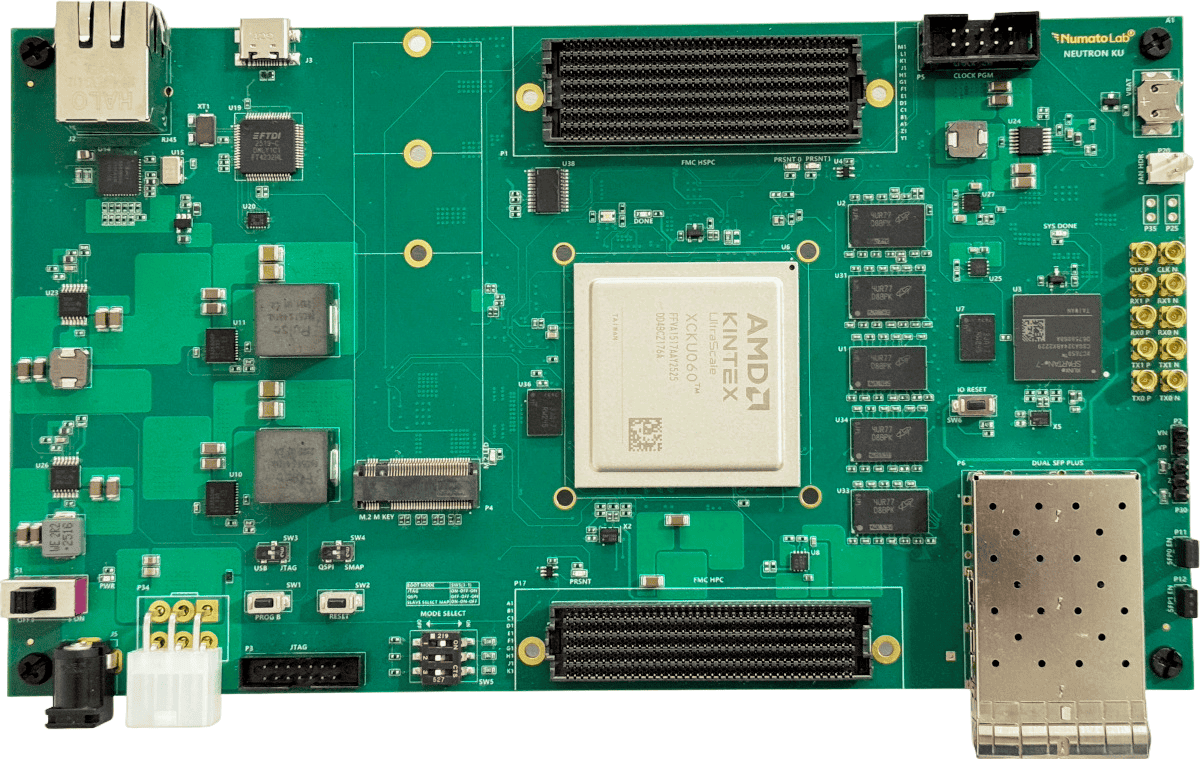

Neutron KU60 FPGA Development Board

The Neutron KU60 FPGA Development Board is a high-performance platform built around the AMD Kintex UltraScale XCKU060 FPGA, designed for demanding high-speed computing, networking, and signal-processing applications. Featuring 4GB ECC-enabled DDR4, dual QSPI configuration memory, multiple clock sources, high-speed SFP+ connectivity, GTH transceiver access, and versatile expansion through FMC+ HSPC, FMC HPC, and an M.2 slot, the board delivers exceptional flexibility for advanced development. With SelectMAP, JTAG/USB programming, and programmable clock options, Neutron KU60 provides a robust and adaptable environment for prototyping and deployment.

Prerequisites:

Hardware:

- The Neutron KU60 FPGA Development Board

- AMD Platform Cable USB or NLJTPRG002

- USB Type C cable

- 12V DC Power Supply (max 5A current rating)

Software:

- Vivado Design Suite 2024.1

- Vitis Classic 2024.1

- Serial Terminal (PuTTY, Tera Term, etc.)

Let’s get started

The following steps will walk you through the process of creating a new project with Vivado and building a hardware platform with MicroBlaze soft processor using an IP integrator. Numato Lab’s Neutron KU60 FPGA Development Board is used in this example, but any compatible FPGA platform can be used with minor changes to the steps. Screenshots are added wherever possible to make the process easier for the reader.

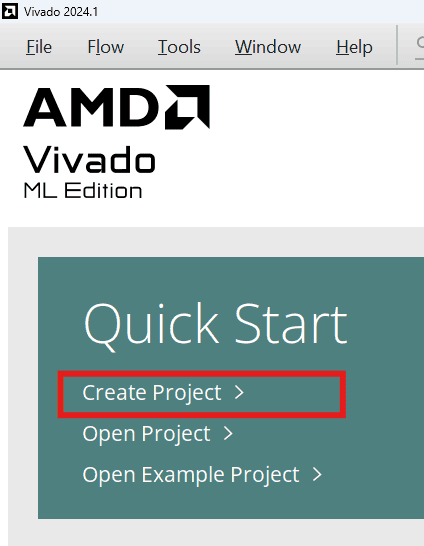

Step 1:

Start Vivado Design Suite, and select “Create Project” from the Quick Start section. The project wizard will pop up. Press Next to proceed with creating the project.

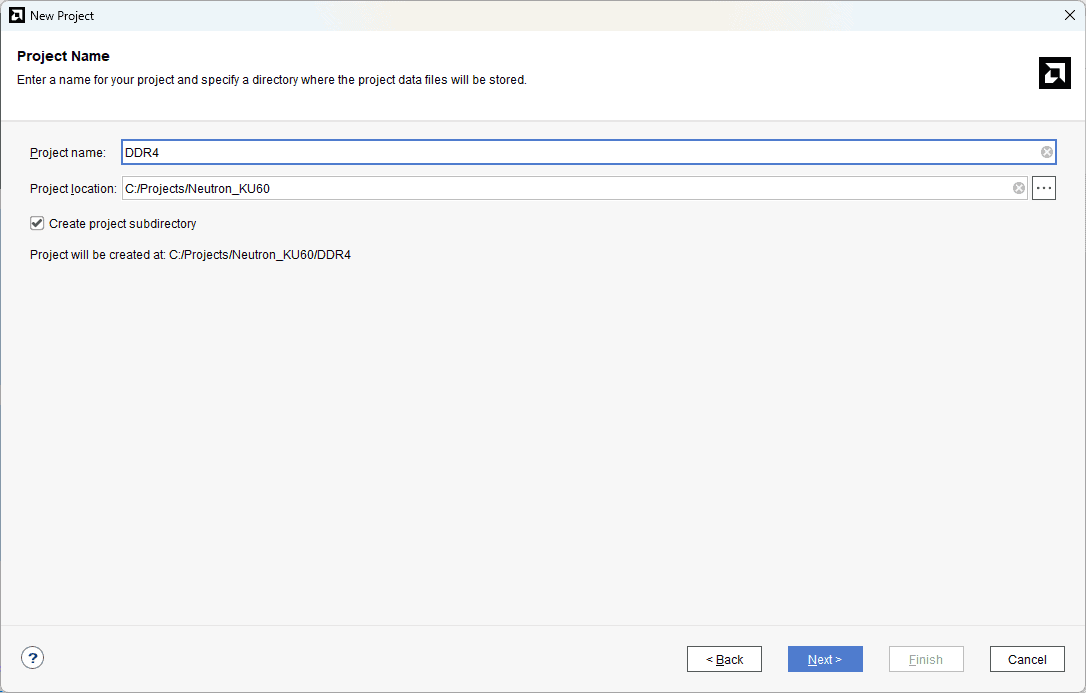

Step 2:

Enter a name for the project and save it at a suitable location. Check the option “Create project subdirectory”. Click Next to continue.

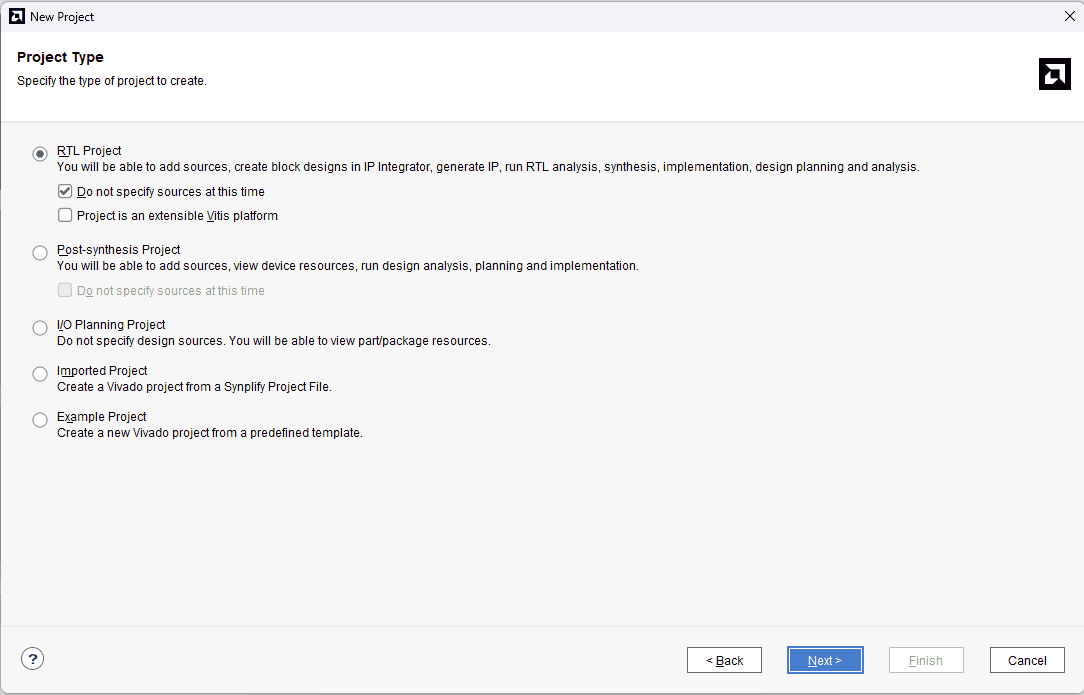

Step 3:

In the Project Type window, select RTL Project and check the option “Do not specify sources at this time”. Click Next.

Step 4:

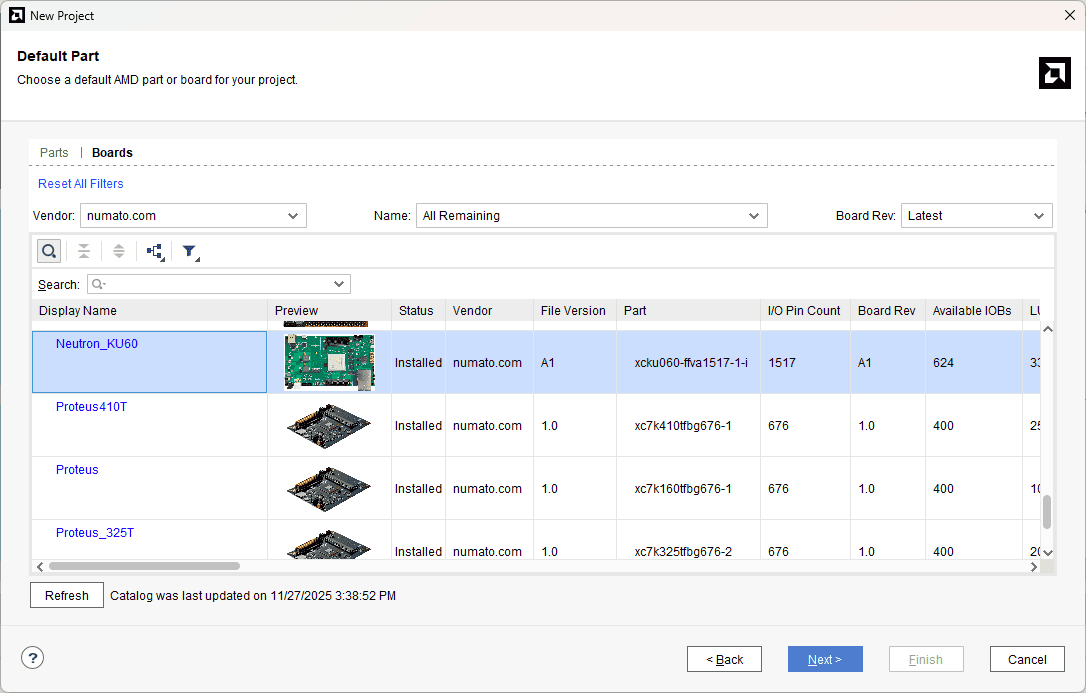

At the “Default Part” stage, switch to the “Boards” tab and set the vendor to numato.com. Select “Neutron_KU60” and click Next. If the Neutron_KU60 does not appear in the list, click “Refresh” to update the board catalog. Vivado will then download the latest board files, after which Neutron_KU60 will become available for selection.

Continue the wizard and finish creating the project. When the new project wizard exits, a new project will be opened up in Vivado with the settings you have selected.

Step 5:

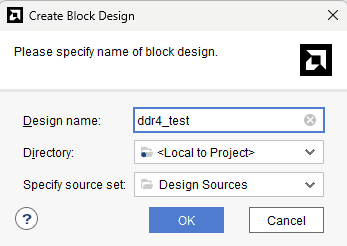

In the Flow Navigator panel, select Create Block Design under IP INTEGRATOR. Enter a name for the block design and click OK. An empty block design will be created.

Step 6:

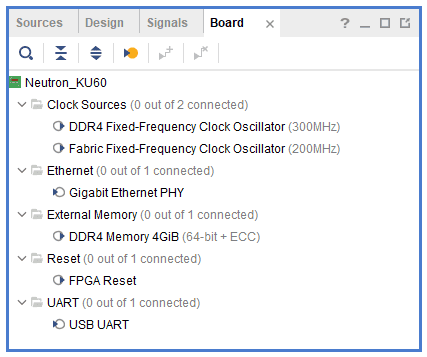

Click the Board tab. The default peripherals available for the Neutron_KU60 will be displayed.

Drag and drop DDR4 Memory 4GiB and USB UART into IP Canvas.

Step 7:

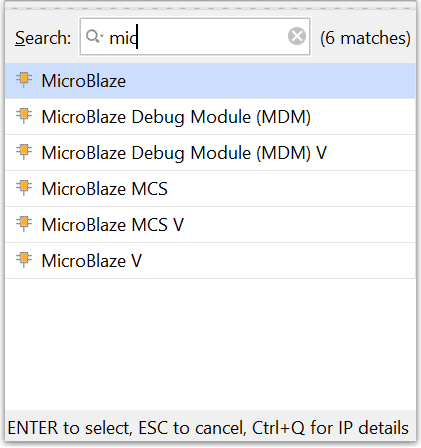

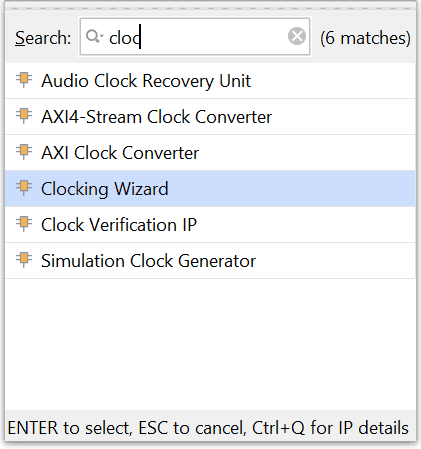

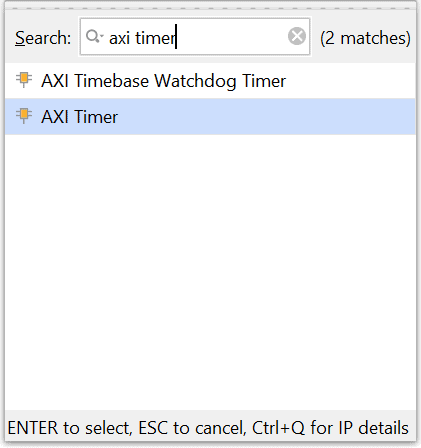

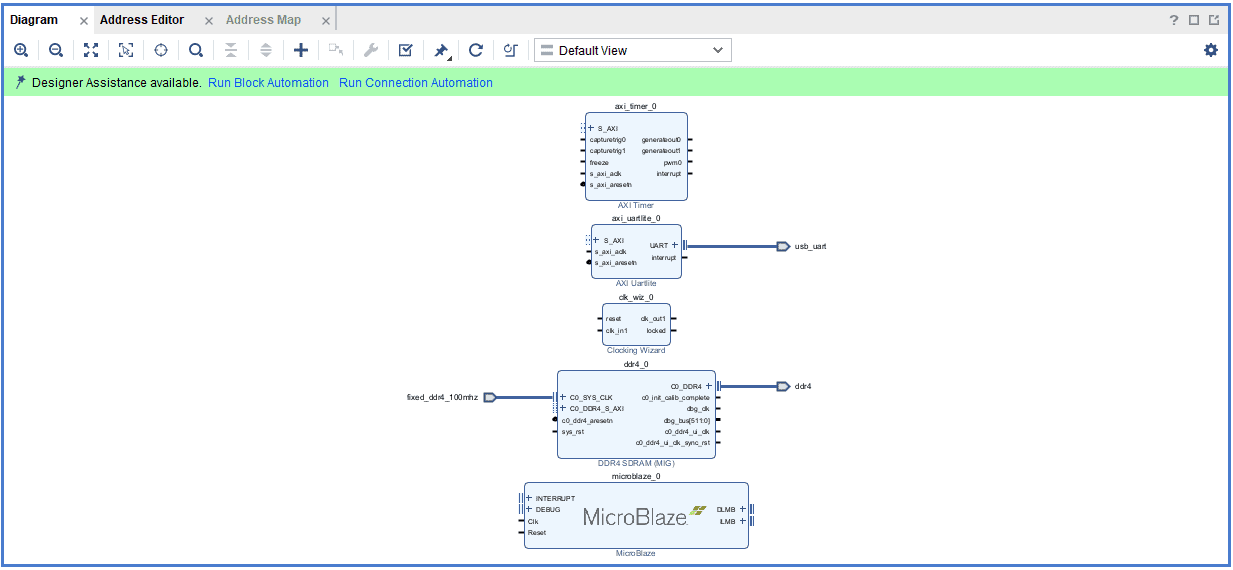

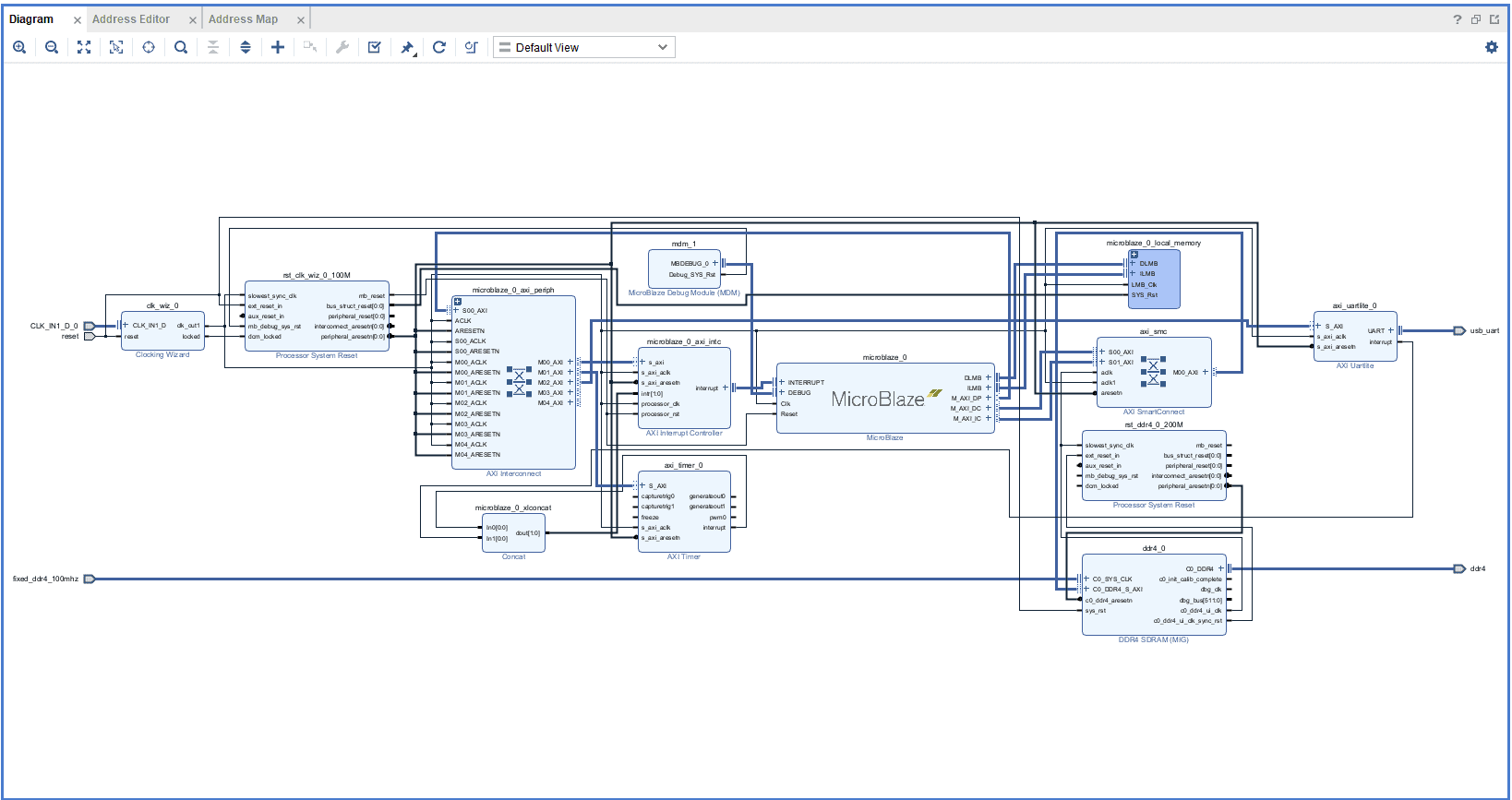

In the Diagram window, right-click and select “Add IP” from the pop-up menu. Search for “MicroBlaze”,” clocking wizard” & “AXI Timer” and add them to the design by double-clicking them.

Step 8:

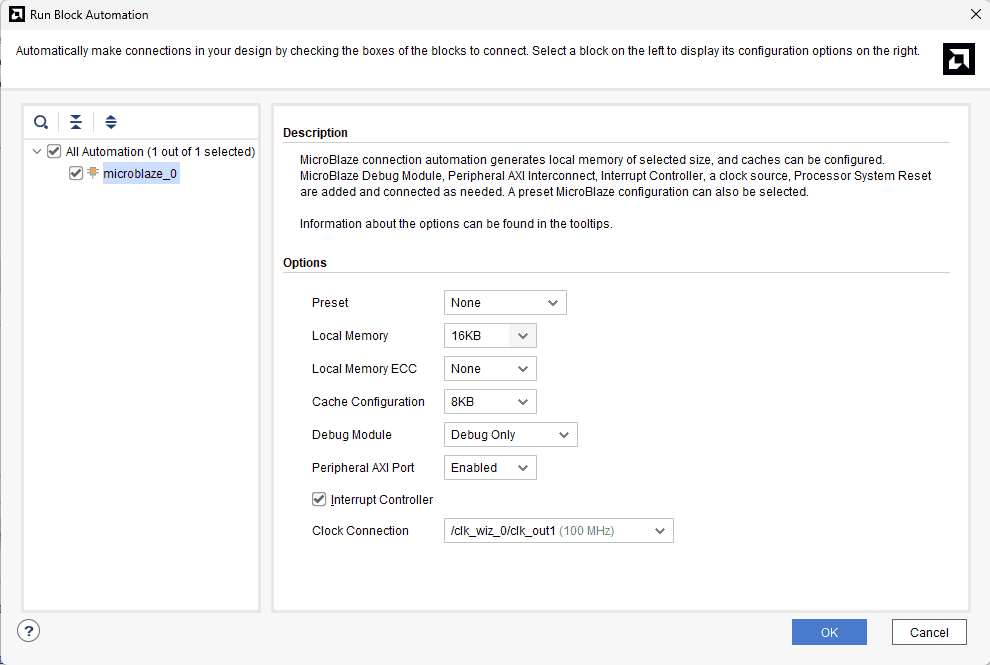

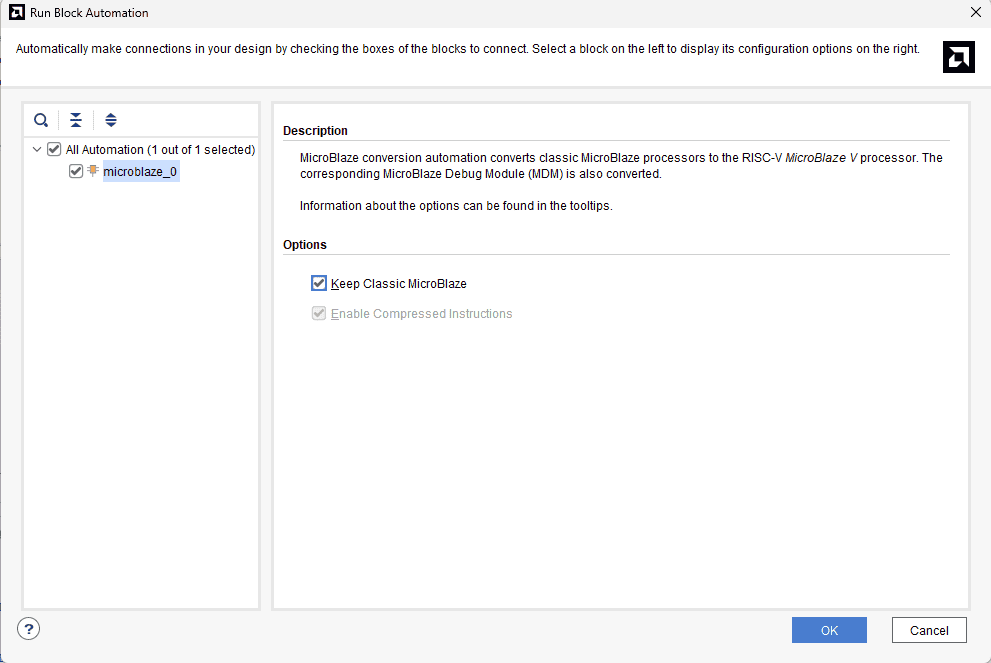

Click “Run Block Automation” present in the “Designer Assistance available” bar on the top left corner of the window to complete the design. Select the settings as shown in the following image. Click “OK” for Vivado to automatically configure the blocks for you. Once Block Automation is complete, run “Connection Automation” so Vivado can connect the blocks to make a complete system.

Enable the “Interrupt controller” in the Run Block Automation Window as below

Step 9:

Connect interrupt output lines from “AXI Timer” and “UARTLite” to the “Concat” block as shown in the figure. Select the “Validate Design” option from the Tools menu to make sure that connections are correct.

Step 10:

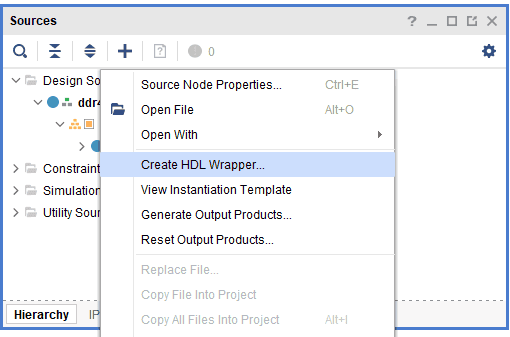

Right-click “ddr4_test” in the “Sources” window, and select “Create HDL Wrapper” from the pop-up menu. Click “OK” on the window that appears to finish generating a wrapper.

Step 11:

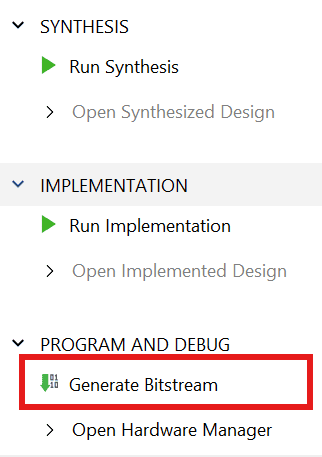

Click “Generate Bitstream” under the “Program and Debug” section to synthesize, implement, and generate a bitstream.

Step 12:

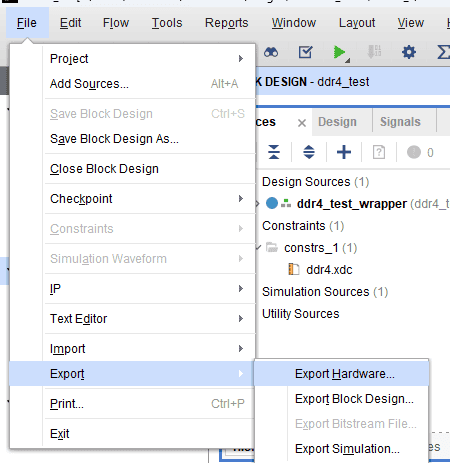

After generating the bitstream successfully, select Export -> Export Hardware from the File menu. Click Next.

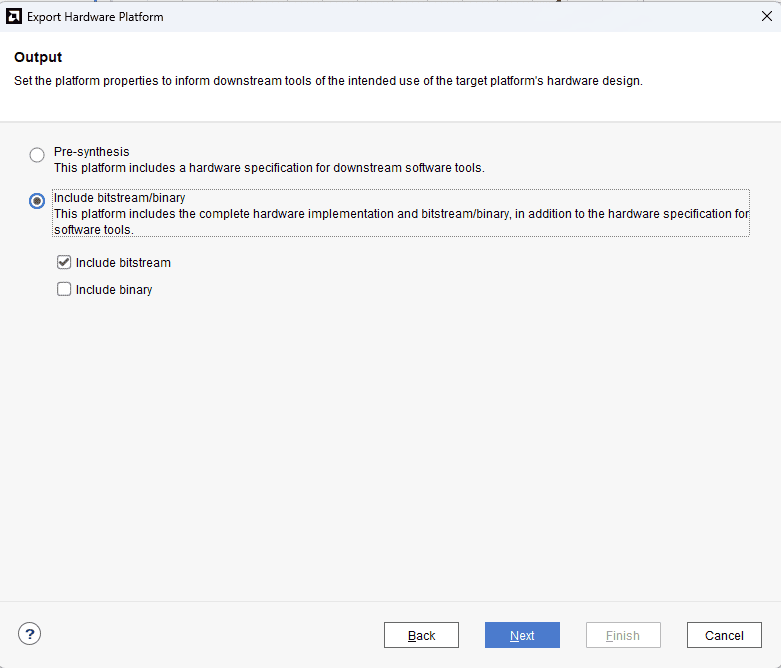

Select the “include bitstream” checkbox and click Next.

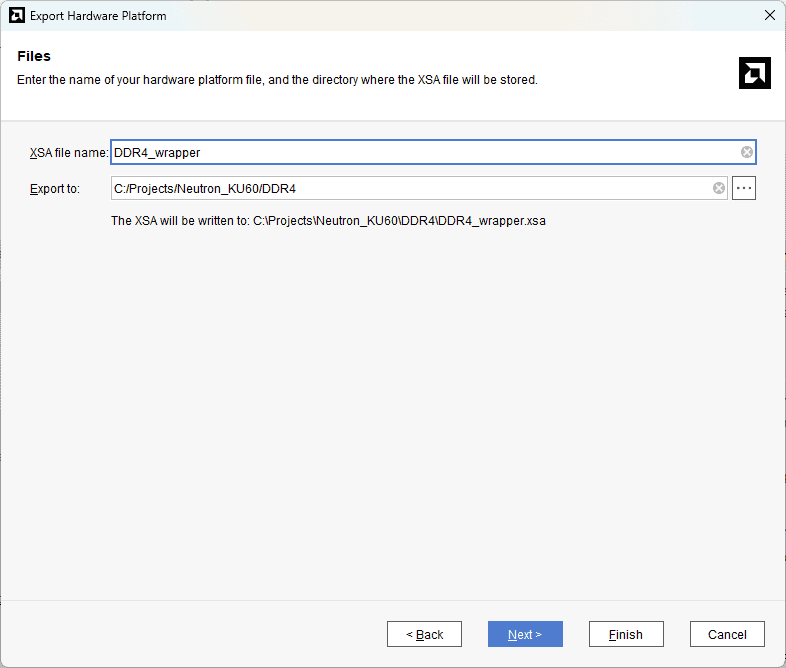

Provide the XSA file name and save it at a suitable location. Click Next and click Finish in the next dialog box.

Step 13:

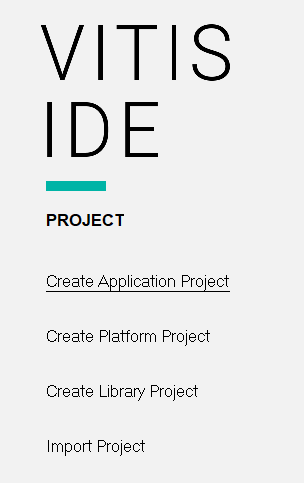

Launch Vitis IDE. In the Vitis IDE window, select Create Application Project and click Next in the dialog box that appears.

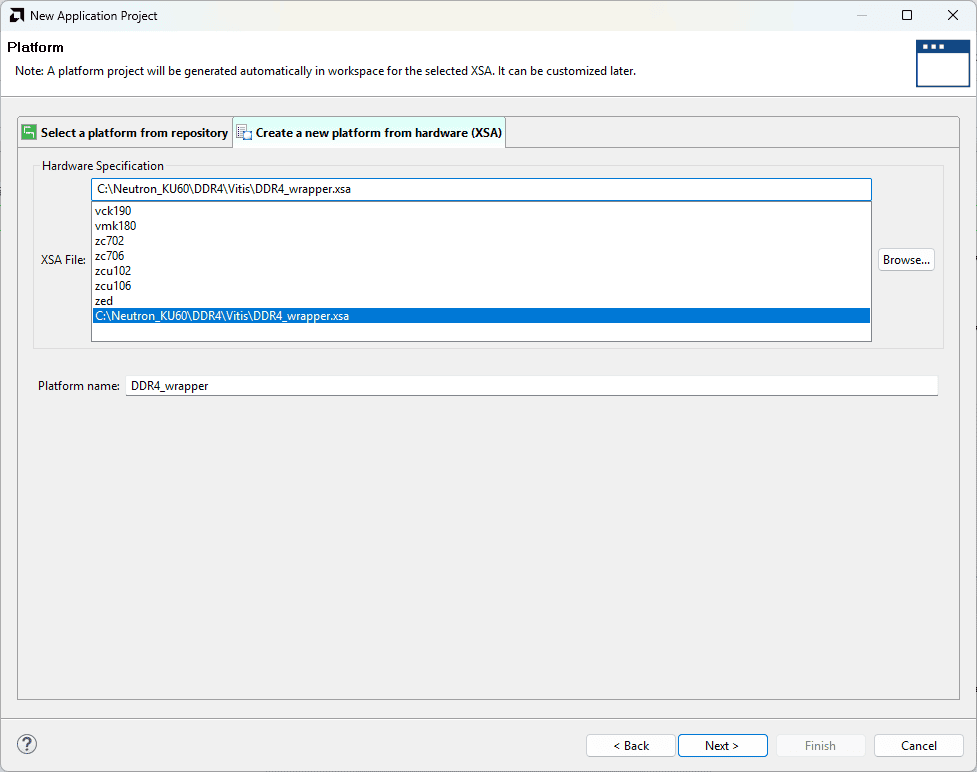

In the Platform window, select Create a new platform from the hardware tab and import the XSA file, which is already created (Provide XSA file location). Click Next.

Step 14:

In the Application Project Details window, give an appropriate name for the Vitis Project and click Next. Click Next in the Domain window.

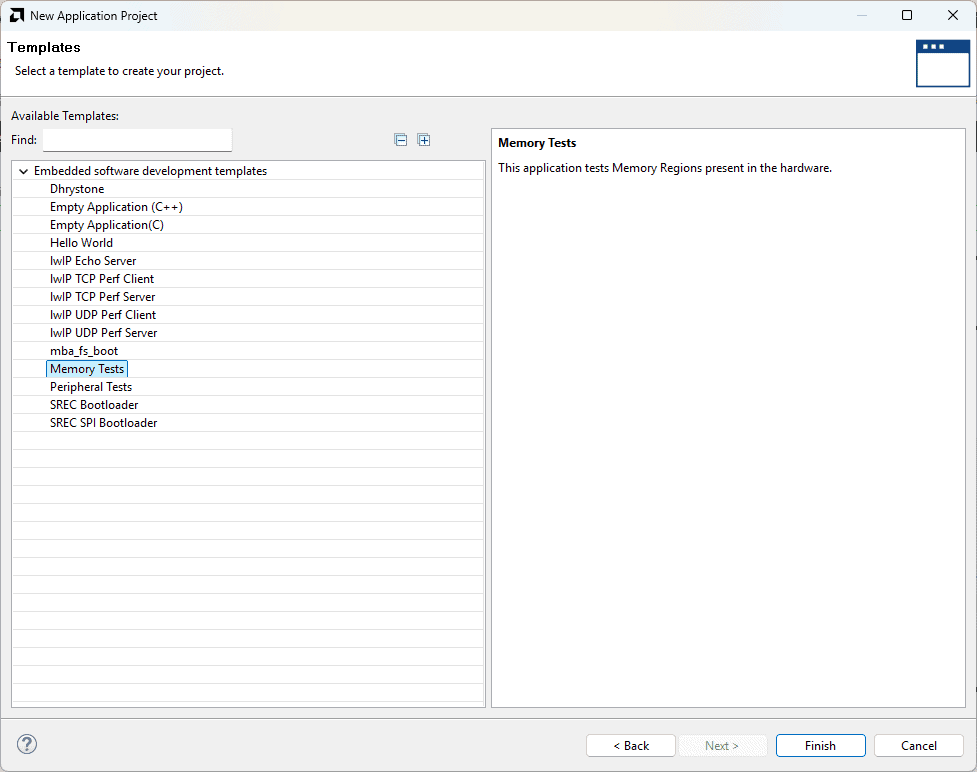

Select the Memory Tests template from the list of available templates and click Finish.

Step 15:

Once the project is created, the Vitis will automatically run a build. If that didn’t happen for any reason, run the build manually. Power up the Neutron KU60 and connect the JTAG or USB-JTAG to the board. Follow the steps mentioned under Programming Neutron KU60 FPGA Development Board Using USB-JTAG in the product user manual. Open any serial terminal program (such as PuTTY, Teraterm, etc.) and open the port corresponding to Neutron KU60 with a 9600 baud rate (the default baud rate given in UART IP).

Step 16:

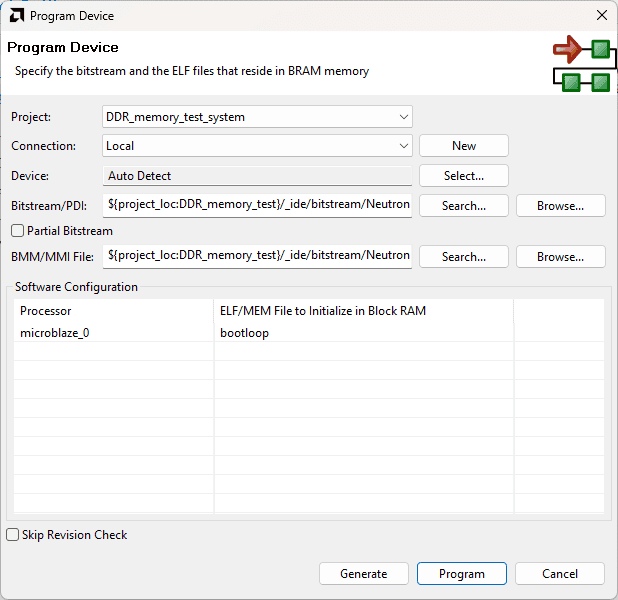

Program the Kintex Ultrascale FPGA on Neutron KU60 with the generated bitstream and simple bootloop firmware by selecting the “Program Device” option from the “Vitis” menu.

Step 17:

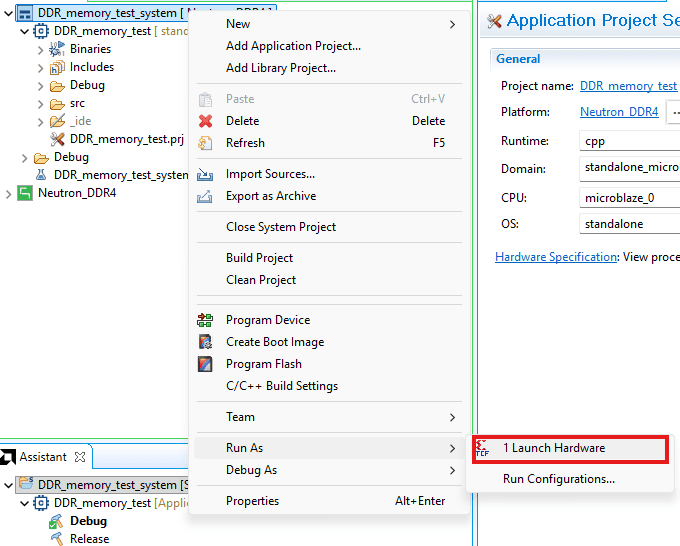

Right-click on the .elf file in the Project Explorer and select “Launch on Hardware” as shown below.

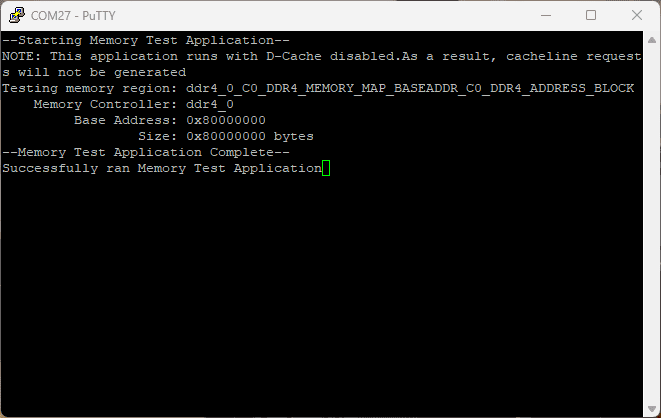

If everything went well, you will see the output below on the Serial Terminal application.

Congratulations on getting your first design running successfully on the Neutron KU60 development Board!