Introduction

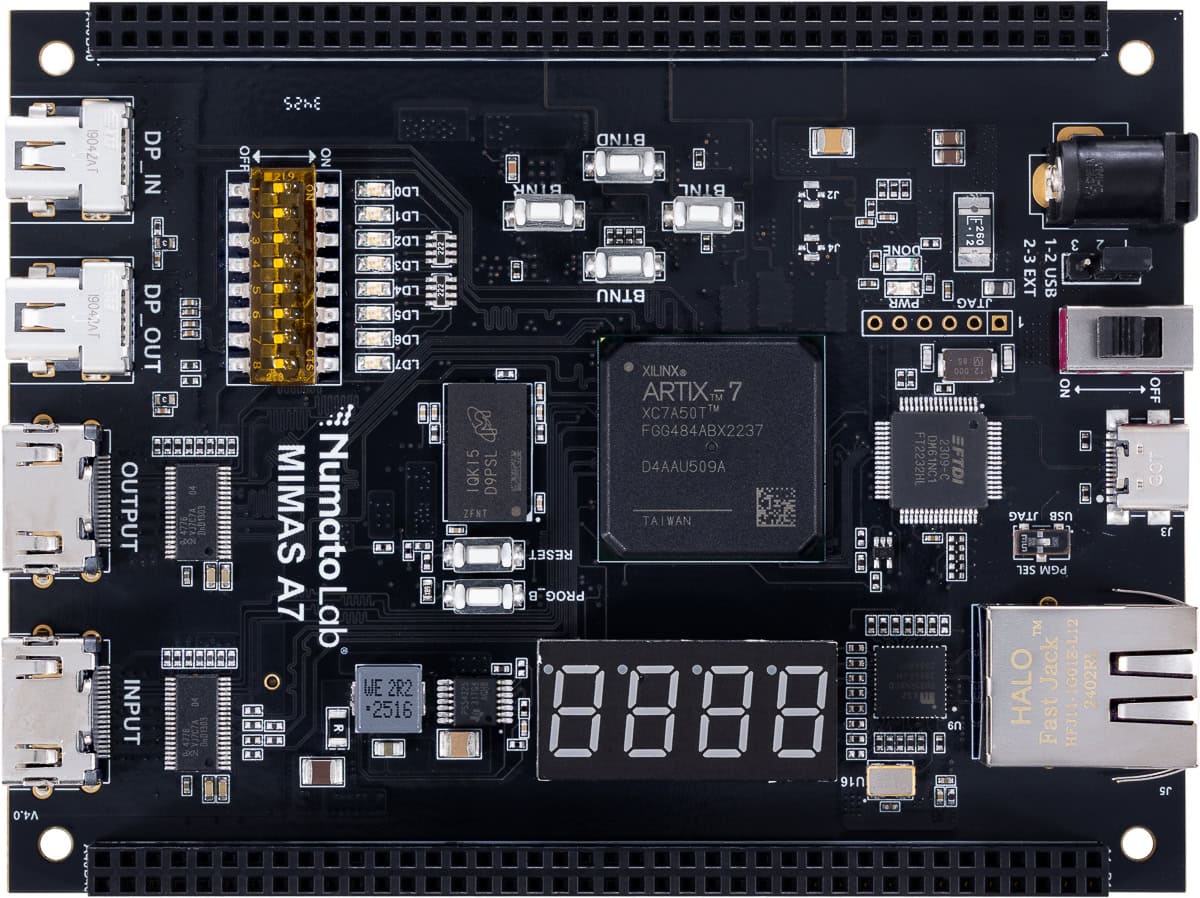

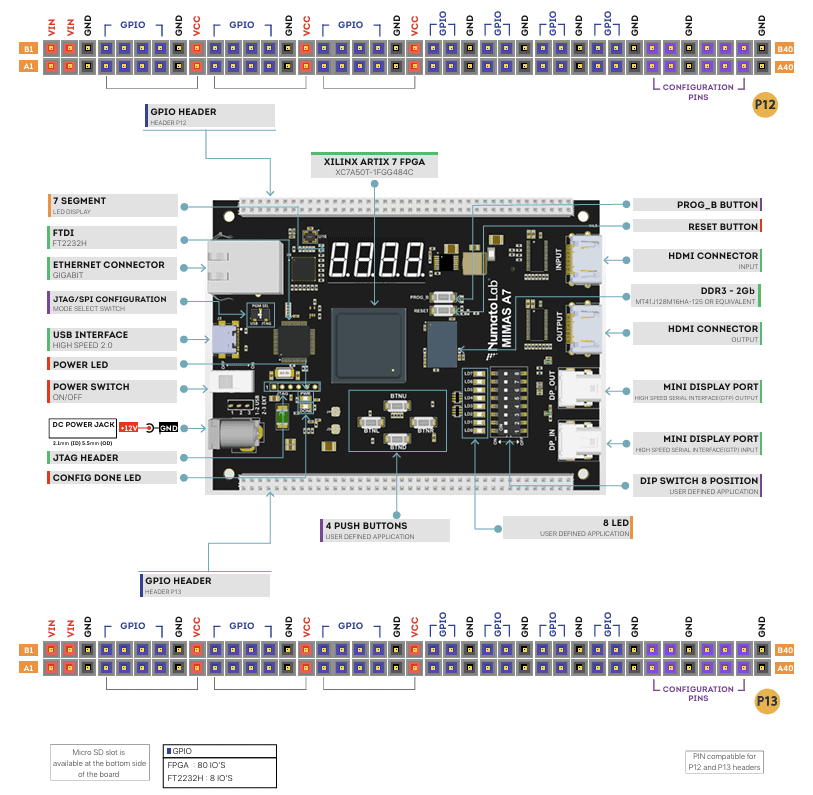

Mimas A7 V4.0 is based on Artix 7™ 50T FPGA. This FPGA Development Board follows the philosophy of offering a large variety of peripherals on a compact form factor to allow minimal external components to run and evaluate as many designs as possible. Mimas A7 V4.0 is a great platform for implementing Soft processors such as Microblaze to make it a complete embedded platform. The built-in Gigabit Ethernet offers low latency high bandwidth data transfer to host. The USB 2.0 host interface based on popular FT2232H offers high bandwidth data transfer and board programming without the need for any external programming adapters. Onboard HDMI IN/OUT interfaces along with large DDR3 SDRAM makes Mimas A7 V4.0 a great platform for video capture, processing, and rendering. The staple peripherals such as switches and seven-segment displays offer great value for learning, prototyping and debugging.

Board Features

- Device: AMD Artix 7 FPGA (XC7A50T-1FGG484C)

- DDR3: 2Gb DDR3 (MT41J128M16HA-125 or equivalent)

- Onboard 128Mb flash memory for FPGA configuration storage and custom user data storage

- 100MHz CMOS oscillator

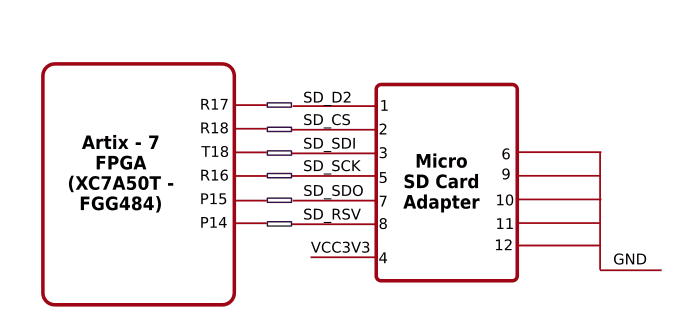

- Micro SD card slot for memory expansion

- Gigabit Ethernet

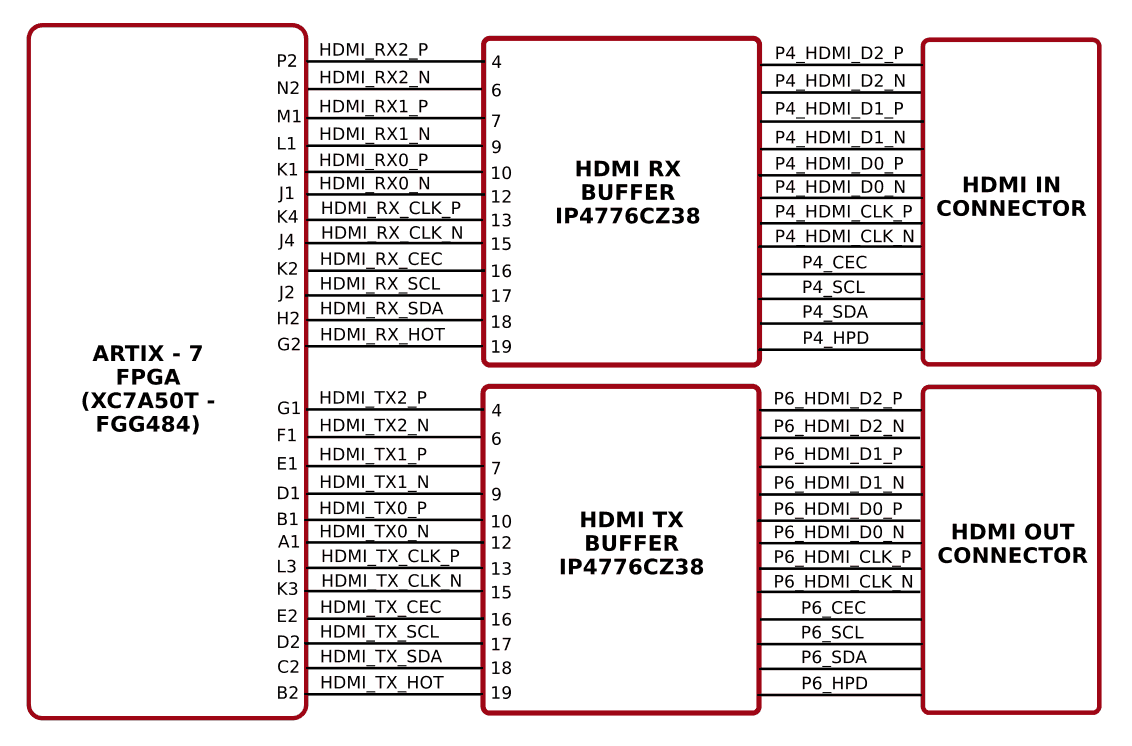

- HDMI IN/OUT interfaces

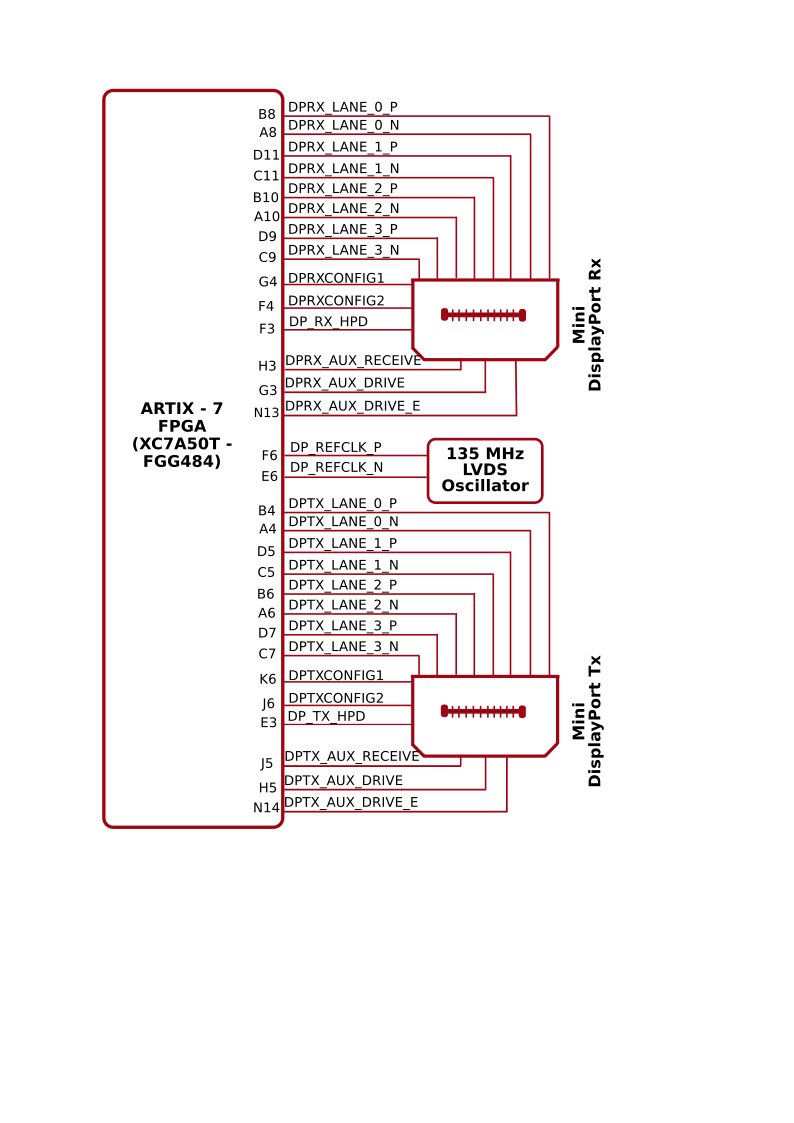

- High-Speed Serial Interface (GTP) available on mini DisplayPort connectors

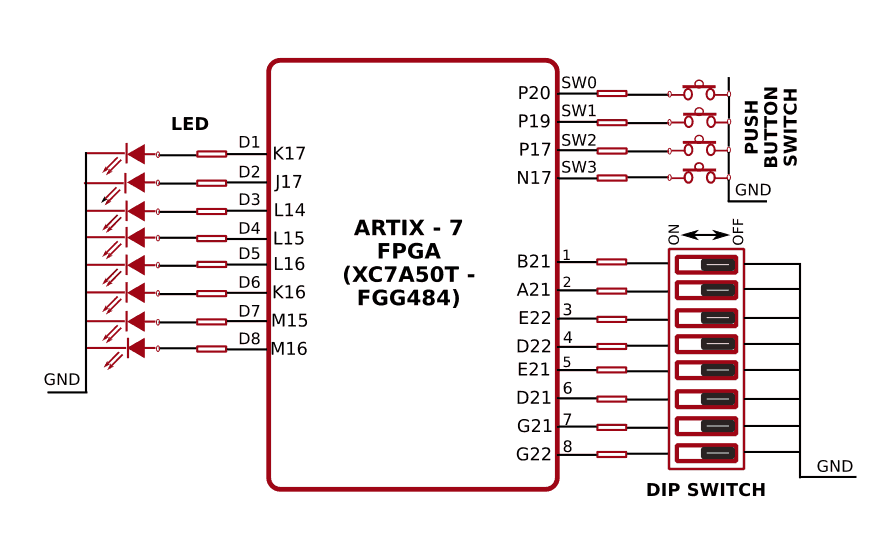

- 8 LEDs, 4 Push Buttons and 8 way DIP switch for user-defined purposes

- FPGA configuration via JTAG and USB

- Maximum IOs for user-defined purposes

- FPGA – 80 IOs (40 professionally length matched Differential Pairs)

Application

- Product Prototype Development

- Accelerated computing integration

- Development and testing of custom embedded processors

- Signal Processing

- Communication devices development

- Educational tool for Schools and Universities

- Video processing

How to use Mimas Artix 7 V4.0 FPGA Development Board

The following sections describe in detail how to use this module.

Hardware Accessories Required

For easy and fast installation, you may need the following items along with the Mimas A7 V4.0 module.

- USB Type-C cable

- DC Power Supply

- AMD Platform Cable USB II compatible JTAG programmer

Wiring Diagram

Revision V4.0:

The following diagram should be used for reference only. The schematics are available at the end of this document for detailed information.

USB Interface

The onboard full-speed USB controller helps a Windows/Linux/Mac computer to communicate with this module. Use a USB-C cable to connect with a PC(the picture on the right shows USB-C connector).

The onboard full-speed USB controller helps a Windows/Linux/Mac computer to communicate with this module. Use a USB-C cable to connect with a PC(the picture on the right shows USB-C connector).

Note: Mimas A7 V4.0 ships with FT2232H Channel A dedicated to JTAG Programming.

Power Select

For Revision V4.0: The Power Selection Header is used to configure the power source for the board. Connect pins 1 and 2 to use USB power and connect pins 2 and 3 to use the external DC power.

PROG_B and Reset Buttons

PROG_B Button

Mimas A7 V4.0 features a Push-button PROG_B normally meant to be used as configuration reset button. Push-button PROG_B is connected to FPGA pin N12. For enabling manual configuration reset, push-button PROG_B is connected to GND. The user can reconfigure the FPGA manually, by pressing this push-button PROG_B.

“PROG_B” is an active-low input pin (pulled up with 4.7K external resistor) to the FPGA and it controls the configuration logic. When the PROG_B pin is de-asserted, resets the FPGA and initializes the new configuration.

Reset Button

Mimas A7 V4.0 features a Push-button RESET normally meant to be used as a “Reset” signal for designs running on FPGA. Push-button RESET is connected to FPGA pin M2. Push-button RESET is active-high. This pushbutton can also be used for any other input and is not just limited to be used as a Reset signal.

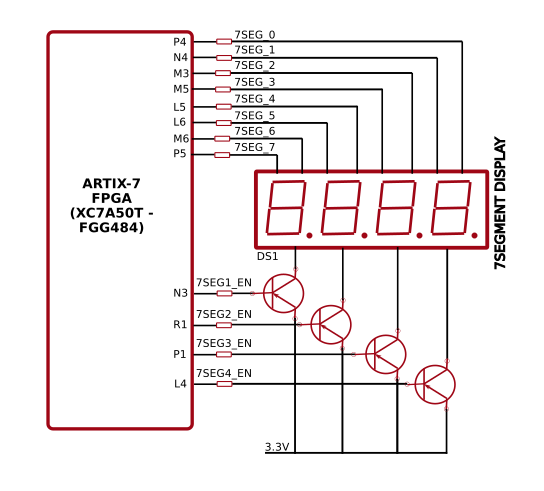

7-Segment LED Display

Revision V4.0:

This version of the board features four 7-segment LED displays. Each module can be separately turned on and off with the four switching transistors.

Note: All signals (a, b, c, d, e, f, g, dot, enable 1, enable 2, enable 3, enable 4) used for controlling 7-Segment display are active-low signals. So, for example, for displaying “8” in display-2, users need to drive Enable 2 to 0 as well as drive signals a, b, c, d, e, f to 0. All other signals need to be driven to 1.

Mini Display Port

Mimas A7 V4.0 includes onboard mini DisplayPort (miniDP or mDP) IN/OUT connectors and it is a miniaturized version of DisplayPort digital display technology. The mini DisplayPort is having four lanes along with auxiliary channel and a hot plug detect the signal. High-Speed Serial Interface (GTP) available on mini DisplayPort connectors.

Revision V4.0:

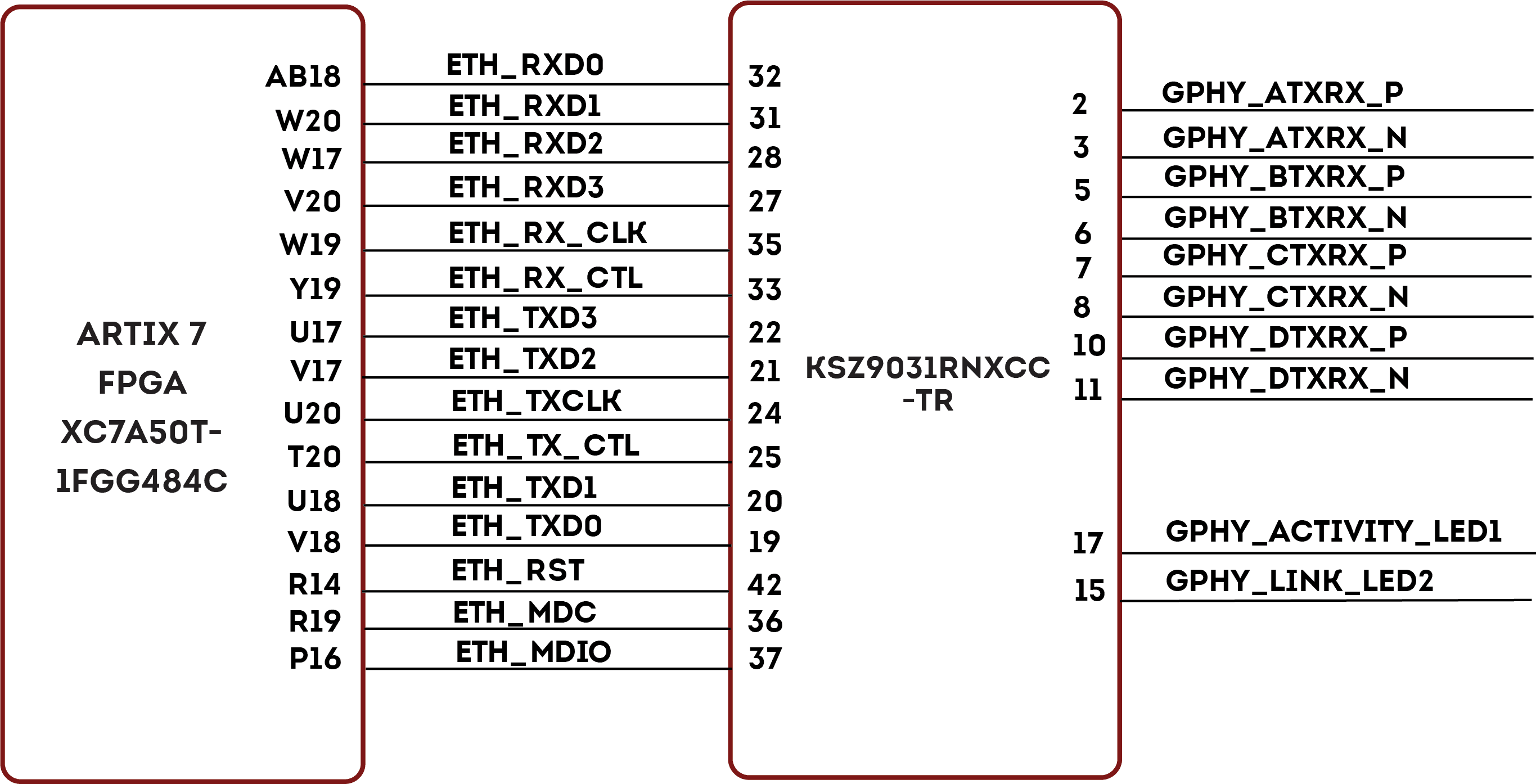

Gigabit Ethernet

Mimas A7 V4.0 Development Board features KSZ9031RNX, a highly integrated Ethernet transceiver from Microchip that complies with 10BASE-T, 100BASE-TX, and 1000Base-T IEEE 802.3 standards. It supports communication with the Ethernet MAC layer via a standard RGMII interface. It contains a high-performance 10/100/1000T transceiver, and the RGMII interface supports 1000Mbps (1Gbps) operation.

GPIOs

This device is equipped with a maximum of 80 user IO pins that can be used for various custom applications. All user IOs are length matched and can be used as differential pairs.

Header P12

| Pin No. On The Header | GPIO Pin Name | Artix-7 (FGG484) Pin No. | Pin No. On The Header | GPIO Pin Name | Artix-7 (FGG484) Pin No. |

|---|---|---|---|---|---|

| A1 | VIN | B1 | VIN | ||

| A2 | VIN | B2 | VIN | ||

| A3 | GND | B3 | GND | ||

| A4 | GPIO_1_P | J20 | B4 | GPIO_1_N | J21 |

| A5 | GPIO_2_P | K21 | B5 | GPIO_2_N | K22 |

| A6 | GPIO_3_P | H20 | B6 | GPIO_3_N | G20 |

| A7 | GPIO_4_P | J19 | B7 | GPIO_4_N | H19 |

| A8 | GND | B8 | GND | ||

| A9 | VCC_VADJ | B9 | VCC_VADJ | ||

| A10 | GPIO_5_P | J22 | B10 | GPIO_5_N | H22 |

| A11 | GPIO_6_P | K18 | B11 | GPIO_6_N | K19 |

| A12 | GPIO_7_P | L19 | B12 | GPIO_7_N | L20 |

| A13 | GPIO_8_P | M21 | B13 | GPIO_8_N | L21 |

| A14 | GND | B14 | GND | ||

| A15 | VCC_VADJ | B15 | VCC_VADJ | ||

| A16 | GPIO_9_P | N22 | B16 | GPIO_9_N | M22 |

| A17 | GPIO_10_P | N20 | B17 | GPIO_10_N | M20 |

| A18 | GPIO_11_P | M18 | B18 | GPIO_11_N | L18 |

| A19 | GPIO_12_P | N18 | B19 | GPIO_12_N | N19 |

| A20 | GND | B20 | GND | ||

| A21 | VCC_VADJ | B21 | VCC_VADJ | ||

| A22 | GPIO_13_P | H17 | B22 | GPIO_13_N | H18 |

| A23 | GPIO_14_P | G17 | B23 | GPIO_14_N | G18 |

| A24 | GND | B24 | GND | ||

| A25 | GPIO_15_P | G15 | B25 | GPIO_15_N | G16 |

| A26 | GPIO_16_P | J15 | B26 | GPIO_16_N | H15 |

| A27 | GND | B27 | GND | ||

| A28 | GPIO_17_P | K13 | B28 | GPIO_17_N | K14 |

| A29 | GPIO_18_P | M13 | B29 | GPIO_18_N | L13 |

| A30 | GND | B30 | GND | ||

| A31 | GPIO_19_P | J14 | B31 | GPIO_19_N | H14 |

| A32 | GPIO_20_P | H13 | B32 | GPIO_20_N | G13 |

| A33 | GND | B33 | GND | ||

| A34 | Vp | L10 | B34 | Vn | M9 |

| A35 | VBAT | E12 | B35 | RESET | M2 |

| A36 | GND | B36 | GND | ||

| A37 | SPI_CS_N | T19 | B37 | SPI_DQ3 | R21 |

| A38 | SPI_DQ1 | R22 | B38 | SPI_SCK | L12 |

| A39 | SPI_DQ2 | P21 | B39 | SPI_DQ0 | P22 |

| A40 | GND | B40 | GND |

Header P13

| Pin No. On The Header | GPIO Pin Name | Artix-7 (FGG484) Pin No. | Pin No. On The Header | GPIO Pin Name | Artix-7 (FGG484) Pin No. |

|---|---|---|---|---|---|

| A1 | VIN | B1 | VIN | ||

| A2 | VIN | B2 | VIN | ||

| A3 | GND | B3 | GND | ||

| A4 | GPIO_21_P | F19 | B4 | GPIO_21_N | F20 |

| A5 | GPIO_22_P | E19 | B5 | GPIO_22_N | D19 |

| A6 | GPIO_23_P | D20 | B6 | GPIO_23_N | C20 |

| A7 | GPIO_24_P | C22 | B7 | GPIO_24_N | B22 |

| A8 | GND | B8 | GND | ||

| A9 | VCC_VADJ | B9 | VCC_VADJ | ||

| A10 | GPIO_25_P | F18 | B10 | GPIO_25_N | E18 |

| A11 | GPIO_26_P | C18 | B11 | GPIO_26_N | C19 |

| A12 | GPIO_27_P | D17 | B12 | GPIO_27_N | C17 |

| A13 | GPIO_28_P | B20 | B13 | GPIO_28_N | A20 |

| A14 | GND | B14 | GND | ||

| A15 | VCC_VADJ | B15 | VCC_VADJ | ||

| A16 | GPIO_29_P | B17 | B16 | GPIO_29_N | B18 |

| A17 | GPIO_30_P | A18 | B17 | GPIO_30_N | A19 |

| A18 | GPIO_31_P | E16 | B18 | GPIO_31_N | D16 |

| A19 | GPIO_32_P | B15 | B19 | GPIO_32_N | B16 |

| A20 | GND | B20 | GND | ||

| A21 | VCC_VADJ | B21 | VCC_VADJ | ||

| A22 | GPIO_33_P | A15 | B22 | GPIO_33_N | A16 |

| A23 | GPIO_34_P | C14 | B23 | GPIO_34_N | C15 |

| A24 | GND | B24 | GND | ||

| A25 | GPIO_35_P | A13 | B25 | GPIO_35_N | A14 |

| A26 | GPIO_36_P | C13 | B26 | GPIO_36_N | B13 |

| A27 | GND | B27 | GND | ||

| A28 | GPIO_37_P | D14 | B28 | GPIO_37_N | D15 |

| A29 | GPIO_38_P | E13 | B29 | GPIO_38_N | E14 |

| A30 | GND | B30 | GND | ||

| A31 | GPIO_39_P | F13 | B31 | GPIO_39_N | F14 |

| A32 | GPIO_40_P | F16 | B32 | GPIO_40_N | E17 |

| A33 | GND | B33 | GND | ||

| A34 | TCK | V12 | B34 | TDO | U13 |

| A35 | TDI | R13 | B35 | TMS | T13 |

| A36 | GND | B36 | GND | ||

| A37 | INIT_B | U12 | B37 | PROGRAM_B | N12 |

| A38 | DONE | G11 | B38 | M0 | U11 |

| A39 | M1 | U10 | B39 | M2 | U9 |

| A40 | GND | B40 | GND |

FT2232H - Artix-7 (FGG484) FPGA Connection Details

| FTDI Pin No. | Pin Function (245 FIFO) | Artix-7 (FGG484) Pin No. |

|---|---|---|

| 38 | FTDI-D0 | Y22 |

| 39 | FTDI-D1 | Y21 |

| 40 | FTDI-D2 | AB22 |

| 41 | FTDI-D3 | AA21 |

| 43 | FTDI-D4 | AB21 |

| 44 | FTDI-D5 | AA20 |

| 45 | FTDI-D6 | AB20 |

| 46 | FTDI-D7 | AA18 |

| 48 | FTDI-RXF# | W21 |

| 52 | FTDI-TXE# | V22 |

| 53 | FTDI-RD# | AA19 |

| 54 | FTDI-WR# | W22 |

| 55 | FTDI-SIWUA | U21 |

Generating Bitstream for Mimas A7 V4.0

The bitstream can be generated for Mimas A7 V4.0 in Vivado by following the steps below:

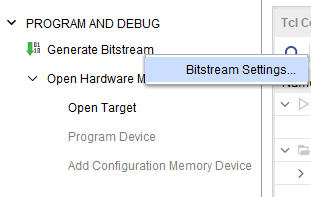

Step 1: It is recommended to generate a .bin bitstream file along with .bit bitstream file. Click “Bitstream Settings”.

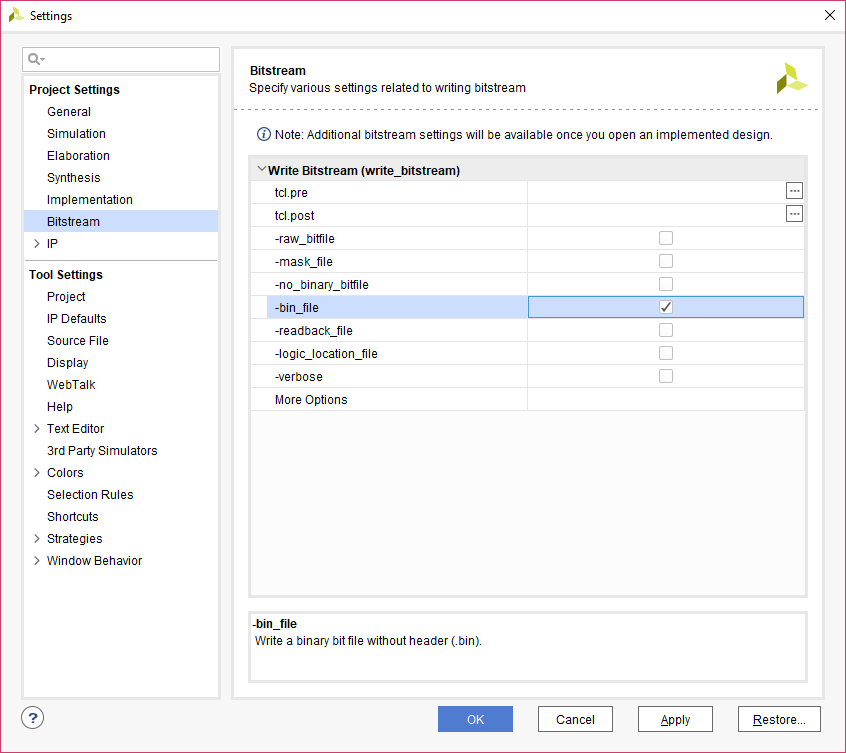

Step 2: In the window that pops up, select the “-bin_file*” option and click OK.

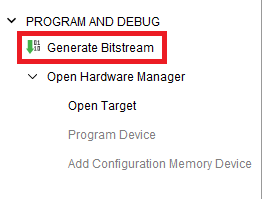

Step 3: Finally click “Generate Bitstream”.

Powering UP Mimas A7 V4.0

Mimas A7 V4.0 can be powered directly from an external supply and there is an option to get powered from the USB also. It is practically very difficult to estimate the power consumption of the board, as it depends heavily on your design and the clock used. AMD provides tools to estimate power consumption. Mimas A7 V4.0 requires three different voltages, a 3.3V, a 1.8V supply, and a 1.2V supply. On-board regulators drive these voltages from the External power supply or USB.

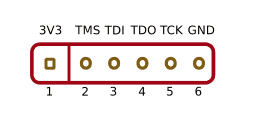

Programming Mimas A7 V4.0 Using JTAG

Set switch PGM_SEL to JTAG for JTAG programming.

Mimas A7 V4.0 FPGA features an onboard JTAG connector which facilitates easy reprogramming of SRAM and onboard SPI flash through a JTAG programmer like “AMD Platform cable USB”. The following steps illustrate how to program Mimas A7 V4.0 using JTAG.

Step1: By using JTAG cable, connect AMD platform cable USB to Mimas A7 and power it up.

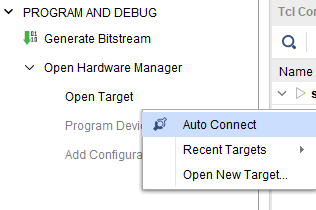

Step2: Open the Vivado project and open the target by clicking on the “Open Target” in “Open Hardware Manager” in the “Program and Debug” section of the Flow Navigator window. Select “Auto Connect”.

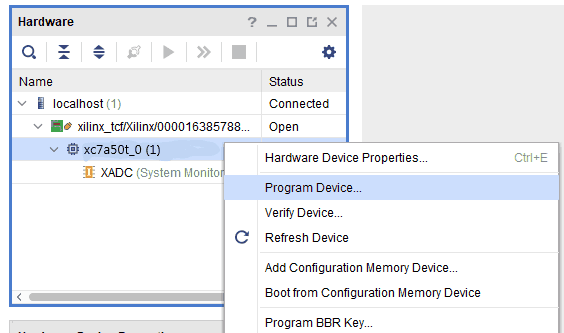

Step3: If the device is detected successfully, then select “Program Device” by right click on the target device “xc7a50t_0” as shown below.

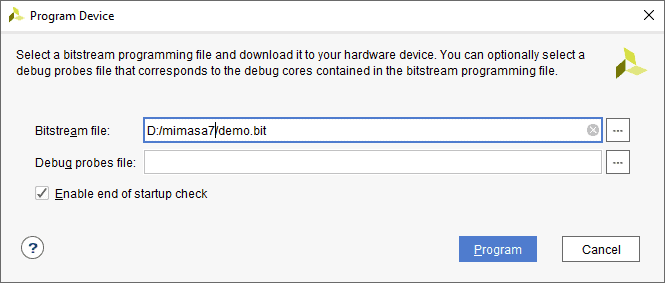

Step4: In the dialog window which opens up, Vivado automatically chooses the correct bitstream file if the design was synthesized, implemented and bitstream generated successfully. If needed, browse to the bitstream which needs to be programmed to FPGA. Finally, click “Program”.

After succesfull programming , the DONE LED will turn off when the configuration is complete.

Programming Mimas A7 V4.0 Using USB-JTAG

Step 1: Ensure that switch PGM_SEL is set to USB and connect the USB Type-C cable to the FPGA board.

Step 2: Click on “Auto connect” under hardware manager, and it will automatically establish the connection.

Step 3: In the dialog window that opens up, Vivado automatically chooses the correct bitstream file if the design was synthesized, implemented, and a bitstream was generated successfully. If needed, browse to the bitstream that needs to be programmed to the FPGA. Finally, click “Program”.

As soon as “Program” is clicked, an Blue coloured DONE LED (DONE) on Mimas A7 V4.0 should light up, indicating that the programming process is going on. This LED will turn off when the configuration is complete.

Programming Mimas A7 V4.0 QSPI Flash using Vivado

A .bin or .mcs file is required for programming Mimas A7 V4.0’s onboard QSPI flash.

Step 1: Open the Vivado project and open the target by clicking on the “Open Target” in “Open Hardware Manager” in the “Program and Debug” section of the Flow Navigator window. Select “Auto Connect”.

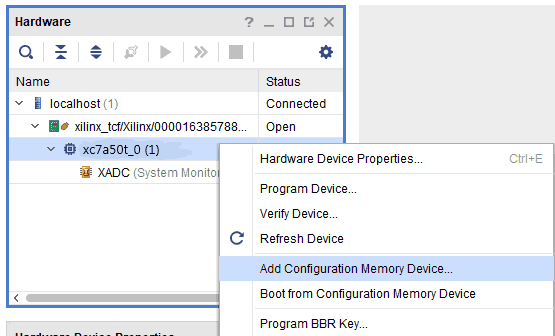

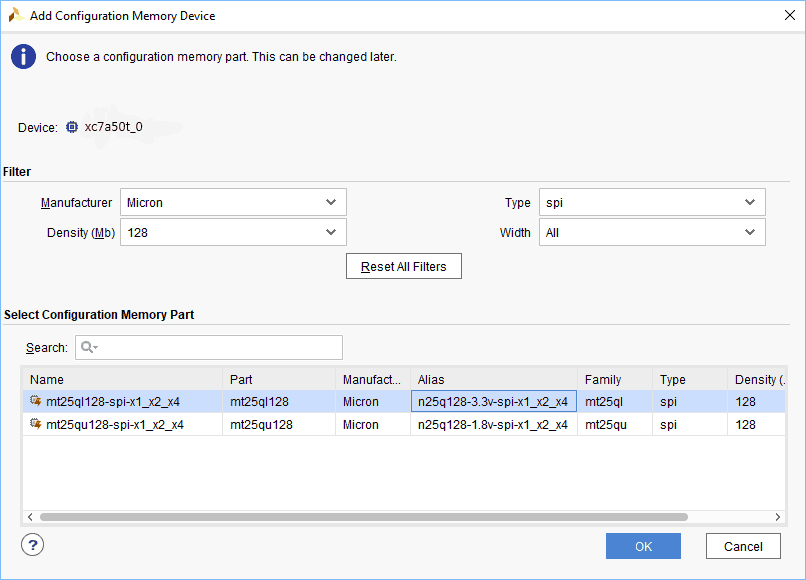

Step 2: If the device is detected successfully, then select “Add Configuration Memory Device” by right click on the target device “xc7a50t_0” as shown below.

Step 3: Select the memory device “mt25ql128-spi-x1_x2_x4 (which is equivalent to n25q128-3.3v-spi-x1_x2_x4)”, then click OK.

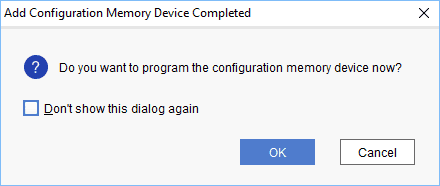

Step 4: After completion of Step 3 the following dialog box will open. Click OK.

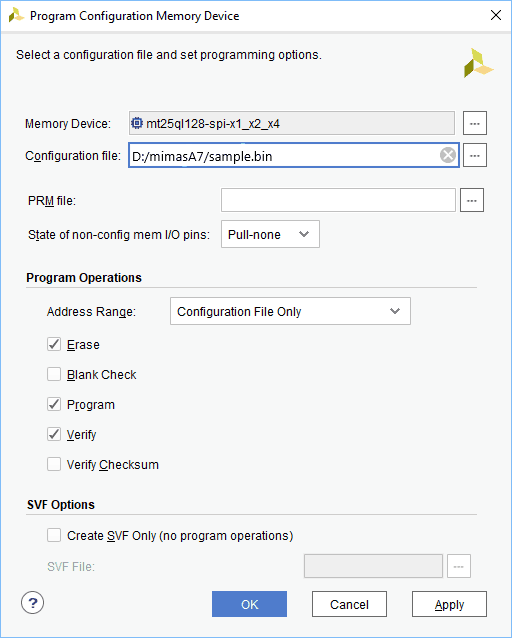

Step 5: Browse to the working .bin file or the .mcs file (whichever applicable) and click OK to program as shown below. If programming is successful, a confirmation message will be displayed.

Technical Specifications

| Parameter * | Value | Unit |

|---|---|---|

| Basic Specifications | ||

| Number of GPIOs | 80 | |

| On-board oscillator frequency (ASEM1-100.000MHZ-LC-T) | 100 | MHz |

| DDR3 SDRAM (MT41J128M16HA - 125 or Equivalent) | 2 | Gb |

| Quad SPI Flash Memory (N25Q128A13ESE40E) | 128 | Mb |

| Power supply voltage (USB or External) | 5 - 12 | V |

| Number of LEDs | 8 | |

| Number of Push Buttons | 4 | |

| Number of Dip Switches | 8 | |

| FPGA Specifications | ||

| Internal supply voltage relative to GND | -0.5 to 1.1 | V |

| Auxiliary supply voltage relative to GND | -0.5 to 2.0 | V |

| Output drivers supply voltage relative to GND | -0.5 to 3.6 | V |

* All parameters considered nominal. Numato Systems Pvt Ltd reserves the right to modify products without notice.