Introduction

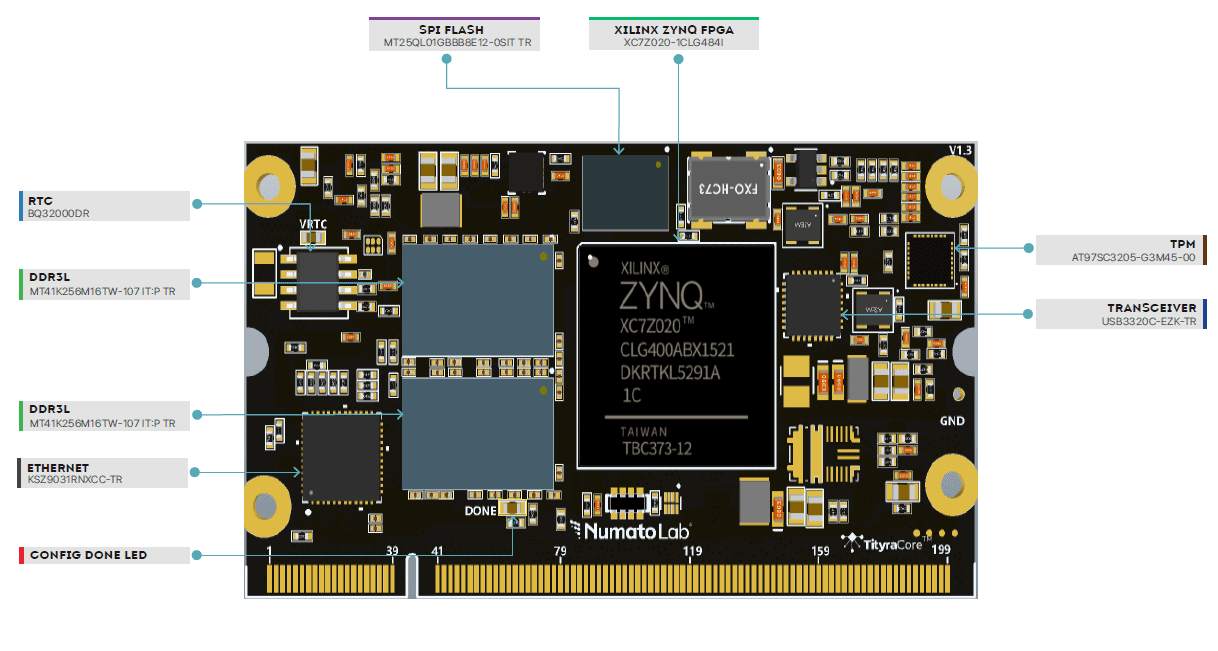

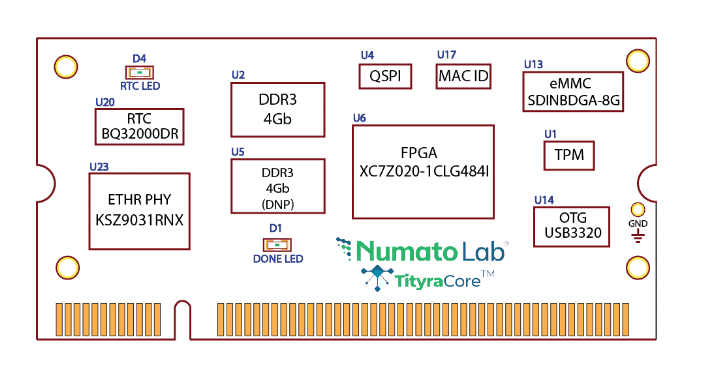

TityraCore Z7 SODIMM incorporates the AMD Zynq XC7Z020 chip, which seamlessly integrates programmable logic with a dual-core ARM Cortex-A9 processor. This integration provides a potent blend of hardware and software processing capabilities, all within a single chip. Zynq series feature a hard System on Chip (SoC) with an ARM core and the range of peripherals offered includes an extensive array of functionalities, such as UARTs, Ethernet controllers, USB ports, timers, interrupt controllers, and various other features. It has a seamless integration of the Processing System(PS) with the Programmable Logic (PL) in which the interaction between them is enabled by a high-bandwidth interface, ensuring communication and efficient data transfer between them. TityraCore Z7 SODIMM is specifically designed for the development and integration of FPGA based accelerated features into other larger designs. It opens up a vast realm of possibilities for implementing innovative solutions across a wide range of applications.

Board Features

- Device: XC7Z020 in CLG484 package, Speed Grade: -1

- SDRAM: 4 Gb DDR3L (MT41K256M16TW-107 IT:P TR or equivalent)

- Flash memory: 1 Gb Quad bit SPI flash memory (MT25QL01GBBB8E12)

- 33 MHz CMOS oscillator

- 50 MHz CMOS oscillator

- Gigabit Ethernet, Real Time Clock, Trusted Platform Module, MAC ID

- High-Speed USB 2.0 OTG interface.

- Flash programming via JTAG and USB

- Micro SD card slot for memory expansion

- 8 GB eMMC

Applications

- Product Prototype Development

- Accelerated computing integration

- Custom Embedded platform

- Signal Processing

- Communication devices development

- Educational tool for Schools and Universities

Reference clock

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 500 | F7 | PS_CLK_500 | 33.33 MHz CLK |

| 34 | B19 | IO_L13P_T2_MRCC_35 | 50 MHz CLK |

Reset

| Bank | Pin No. | Signal name | Function |

|---|---|---|---|

| 501 | C9 | PS_SRST_B_501 | n RST IN |

| 500 | B5 | PS_POR_B_500 | Program B |

DDR3L SDRAM

TityraCore SODIMM includes DDR3L memory technology which is the third generation of DDR memory technology designed to operate at lower voltage levels (1.35 V) compared to standard DDR3 modules. TityraCore SODIMM uses micron MT41K256M16TW-107 IT:P TR memory which has a capacity of 4 Gb of RAM. DDR3L is connected to PS section of Zynq-7000 AP SoC and has the speed up to 1866 MT/s.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 502 | D1 | PS_DDR_DQ0_502 | DDR-DQ0 |

| 502 | C3 | PS_DDR_DQ1_502 | DDR-DQ1 |

| 502 | B2 | PS_DDR_DQ2_502 | DDR-DQ2 |

| 502 | D3 | PS_DDR_DQ3_502 | DDR-DQ3 |

| 502 | E3 | PS_DDR_DQ4_502 | DDR-DQ4 |

| 502 | E1 | PS_DDR_DQ5_502 | DDR-DQ5 |

| 502 | F2 | PS_DDR_DQ6_502 | DDR-DQ6 |

| 502 | F1 | PS_DDR_DQ7_502 | DDR-DQ7 |

| 502 | G2 | PS_DDR_DQ8_502 | DDR-DQ8 |

| 502 | G1 | PS_DDR_DQ9_502 | DDR-DQ9 |

| 502 | L1 | PS_DDR_DQ10_502 | DDR-DQ10 |

| 502 | L2 | PS_DDR_DQ11_502 | DDR-DQ11 |

| 502 | L3 | PS_DDR_DQ12_502 | DDR-DQ12 |

| 502 | K1 | PS_DDR_DQ13_502 | DDR-DQ13 |

| 502 | J1 | PS_DDR_DQ14_502 | DDR-DQ14 |

| 502 | K3 | PS_DDR_DQ15_502 | DDR-DQ15 |

| 502 | M4 | PS_DDR_A0_502 | DDR0-A0 |

| 502 | M5 | PS_DDR_A1_502 | DDR0-A1 |

| 502 | K4 | PS_DDR_A2_502 | DDR0-A2 |

| 502 | L4 | PS_DDR_A3_502 | DDR0-A3 |

| 502 | K6 | PS_DDR_A4_502 | DDR0-A4 |

| 502 | K5 | PS_DDR_A5_502 | DDR0-A5 |

| 502 | J7 | PS_DDR_A6_502 | DDR0-A6 |

| 502 | J6 | PS_DDR_A7_502 | DDR0-A7 |

| 502 | J5 | PS_DDR_A8_502 | DDR0-A8 |

| 502 | H5 | PS_DDR_A9_502 | DDR0-A9 |

| 502 | J3 | PS_DDR_A10_502 | DDR0-A10 |

| 502 | G5 | PS_DDR_A11_502 | DDR0-A11 |

| 502 | H4 | PS_DDR_A12_502 | DDR0-A12 |

| 502 | F4 | PS_DDR_A13_502 | DDR0-A13 |

| 502 | G4 | PS_DDR_A14_502 | DDR0-A14 |

| 502 | L7 | PS_DDR_BA0_502 | DDR-BA0 |

| 502 | L6 | PS_DDR_BA1_502 | DDR-BA1 |

| 502 | M6 | PS_DDR_BA2_502 | DDR-BA2 |

| 502 | P6 | PS_DDR_CS_B_502 | DDR0-CS# |

| 502 | R5 | PS_DDR_RAS_B_502 | DDR0-RAS |

| 502 | P3 | PS_DDR_CAS_B_502 | DDR0-CAS |

| 502 | R4 | PS_DDR_WE_B_502 | DDR0-WE |

| 502 | N5 | PS_DDR_CKN_502 | DDR0-CK N |

| 502 | N4 | PS_DDR_CKP_502 | DDR0-CK P |

| 502 | V3 | PS_DDR_CKE_502 | DDR0-CKE |

| 502 | F3 | PS_DDR_DRST_B_502 | DDR0-RESET |

| 502 | P5 | PS_DDR_ODT_502 | DDR0-ODT |

| 502 | B1 | PS_DDR_DM0_502 | DDR-DM0 |

| 502 | H3 | PS_DDR_DM1_502 | DDR-DM1 |

| 502 | C2 | PS_DDR_DQS_P0_502 | DDR_DQS0 P |

| 502 | D2 | PS_DDR_DQS_N0_502 | DDR_DQS0 N |

| 502 | H2 | PS_DDR_DQS_P1_502 | DDR_DQS1 P |

| 502 | J2 | PS_DDR_DQS_N1_502 | DDR_DQS1 N |

QSPI Flash

The TityraCore SODIMM has 1 Gb of Quad bit SPI flash memory. It is a serial NOR flash which operates at the voltage of 3.3 V. It is connected to QSPI controller of the PS and serves as the default primary boot device. Memory size of QSPI flash memory can be expanded to 8GB using eMMC flash.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 500 | A1 | PS_MIO1_500 | SPI_CS_N |

| 500 | A2 | PS_MIO2_500 | SPI_DQ[0] |

| 500 | F6 | PS_MIO3_500 | SPI_DQ[1] |

| 500 | E4 | PS_MIO4_500 | SPI_DQ[2] |

| 500 | A3 | PS_MIO5_500 | SPI_DQ[3] |

| 500 | A4 | PS_MIO6_500 | SPI_SCK |

Micro SD Card

The TityrCore SODIMM have micro-SD card feature that can be incorporated in the carrier board. SD Card can be used to store non-volatile external memory. It is directly connected to the SD0 controller of the PS MIO bank and operates at 1.8 V.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 501 | E14 | PS_MIO40_501 | SD0_CLK |

| 501 | C8 | PS_MIO41_501 | SD0_CMD |

| 501 | D8 | PS_MIO42_501 | SD0_DAT0 |

| 501 | B11 | PS_MIO43_501 | SD0_DAT1 |

| 501 | E13 | PS_MIO44_501 | SD0_DAT2 |

| 501 | B9 | PS_MIO45_501 | SD0_DAT3 |

eMMC Flash

TityraCore SODIMM supports 8 Gb of eMMC flash memory for additional storage. It operates at a voltage level of 3.3 V and is connected to sd1 controller of the PS MIO bank . It can serve as a means to increase the capacity of SPI flash memory and function as a secondary boot device.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 500 | G7 | PS_MIO10_500 | eMMC_DAT0 |

| 500 | B4 | PS_MIO11_500 | eMMC_CMD |

| 500 | C5 | PS_MIO12_500 | eMMC_CLK |

| 500 | A6 | PS_MIO13_500 | eMMC_DAT1 |

| 500 | B6 | PS_MIO14_500 | eMMC_DAT2 |

| 500 | E6 | PS_MIO15_500 | eMMC_DAT3 |

Ethernet

TityraCore SODIMM implements single-Chip 10/100/1000 Mbps Ethernet Transceiver, with 1.8 V IO operating voltage using Gigabit ethernet PHY “KSZ9031RNX”. It provides the Reduced Gigabit Media Independent Interface (RGMII) and is connected to the Gigabit Ethernet controller of PS MIO bank in Zynq-7000 AP SOC.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 501 | D6 | PS_MIO16_501 | ETH_TXCLK |

| 501 | E9 | PS_MIO17_501 | ETH_TXD0 |

| 501 | A7 | PS_MIO18_501 | ETH_TXD1 |

| 501 | E10 | PS_MIO19_501 | ETH_TXD2 |

| 501 | A8 | PS_MIO20_501 | ETH_TXD3 |

| 501 | F11 | PS_MIO21_501 | ETH_TXCTL |

| 501 | A14 | PS_MIO22_501 | ETH_RXCLK |

| 501 | E11 | PS_MIO23_501 | ETH_RXD0 |

| 501 | B7 | PS_MIO24_501 | ETH_RXD1 |

| 501 | F12 | PS_MIO25_501 | ETH_RXD2 |

| 501 | A13 | PS_MIO26_501 | ETH_RXD3 |

| 501 | D7 | PS_MIO27_501 | ETH_RXCTL |

| 501 | D10 | PS_MIO52_501 | ETH_MDC |

| 501 | C12 | PS_MIO53_501 | ETH_MDIO |

USB 2.0 OTG

TityraCore SODIMM support high speed USB 2.0 On-The-Go (OTG) transceiver with 24 MHz operating frequency. TityraCore SODIMM uses “USB3320” ULPI transceiver and supports both device and host modes. The ULPI (UTMI+ Low Pin Interface) protocol is utilized to establish a connection between MIO (Multi-Function Input/Output) pins and the PHY (Physical Layer) component. It is connected to the OTG controller of PS MIO bank and works at 1.8V voltage.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 501 | A12 | PS_MIO28_501 | USB_D4 |

| 501 | E8 | PS_MIO29_501 | USB_DIR |

| 501 | A11 | PS_MIO30_501 | USB_STP |

| 501 | F9 | PS_MIO31_501 | USB_NXT |

| 501 | C7 | PS_MIO32_501 | USB_D0 |

| 501 | G13 | PS_MIO33_501 | USB_D1 |

| 501 | B12 | PS_MIO34_501 | USB_D2 |

| 501 | F14 | PS_MIO35_501 | USB_D3 |

| 501 | A9 | PS_MIO36_501 | USB_CLK |

| 501 | B14 | PS_MIO37_501 | USB_D5 |

| 501 | F13 | PS_MIO38_501 | USB_D6 |

| 501 | C13 | PS_MIO39_501 | USB_D7 |

Trusted Platform Module

The Trusted Platform Module(TPM) is an integrated security module for hardware authentication. The security module is used primarily for cryptographic key generation, key storage and key management as well as generation and secure storage for digital certificates.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 33 | W16 | IO_L14P_T2_SRCC_33 | TPM_CLK |

| 33 | Y16 | IO_L14N_T2_SRCC_33 | TPM_CS# |

| 33 | U15 | IO_L15P_T2_DQS_33 | TPM_RST# |

| 33 | U16 | IO_L15N_T2_DQS_33 | TPM_MISO |

| 33 | U17 | IO_L16P_T2_33 | TPM_MOSI |

Real Time Clock

TityraCore SODIMM includes Real Time Clock (RTC), an integral part of electronic devices that operates independently of the device to accurately track real-world time. It is connected to PL Bank33 and has an operating voltage of 3.3 V.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 34 | W17 | IO_L13P_T2_MRCC_33 | RT_SCL |

| 34 | W18 | IO_L13N_T2_MRCC_33 | RT_SDA |

MAC EEPROM

TityraCore SODIMM features MAC ID EEPROM, which is a memory chip that stores the unique MAC address of a network interface. It is a non-volatile memory that interfaces with PL Bank13 of Zynq-7000 AP SoC. It operates at a voltage of 3.3 V.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 13 | V7 | IO_L23P_T3_13 | MAC_SCL |

| 13 | W7 | IO_L23N_T3_13 | MAC_SDA |

UART

TityraCore SODIMM have UART interface connected to PS UART controller peripheral of the device. UART offer a flexible and user-friendly solution for incorporating serial communication interfaces, facilitating seamless data exchange with external devices across a diverse array of applications.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 501 | D13 | PS_MIO50_501 | UART_RX |

| 501 | C10 | PS_MIO51_501 | UART_TX |

I2C

TityraCore SODIMM offers I2C communication through PS I2C controller and offers a flexible and efficient solution for establishing communication with various peripheral devices using the I2C protocol. It has a operating voltage of 1.8 V.

| Bank | Pin No. | Signal Name | Function |

|---|---|---|---|

| 501 | D12 | PS_MIO46_501 | I2C_SCL |

| 501 | B10 | PS_MIO47_501 | I2C_SDA |

Header P1

| Bank | Pin No | Signal name | function |

|---|---|---|---|

| 35 | G17 | IO_L6P_T0_35 | P1_1 |

| 13 | U9 | IO_L6N_T0_VREF_13 | P1_2 |

| 35 | F17 | IO_L6N_T0_VREF_35 | P1_3 |

| 34 | P15 | IO_L19N_T3_VREF_34 | P1_4 |

| 35 | H19 | IO_L19P_T3_35 | P1_5 |

| 35 | H20 | IO_L19N_T3_VREF_35 | P1_6 |

| 34 | H15 | IO_0_34 | P1_7 |

| 34 | L16 | IO_L3N_T0_DQS_34 | P1_8 |

Header P2

| Bank | Pin No | Signal Name | Function |

|---|---|---|---|

| 34 | N15 | IO_L19P_T3_34 | P2_1 |

| 34 | M20 | IO_L13N_T2_MRCC_34 | P2_2 |

| 35 | D22 | IO_L16P_T2_35 | P2_3 |

| 35 | C22 | IO_L16N_T2_35 | P2_4 |

| 34 | R15 | IO_25_34 | P2_5 |

| 34 | R16 | IO_L24N_T3_34 | P2_6 |

| 34 | M15 | IO_L6P_T0_34 | P2_7 |

| 34 | M16 | IO_L6N_T0_VREF_34 | P2_8 |

GPIO

| Bank | Pin No. | Signal Name |

|---|---|---|

| 13 | AA9 | PL_IO_L11_T1_SRCC_13_P |

| 13 | AA8 | PL_IO_L11_T1_SRCC_13_N |

| 13 | Y9 | PL_IO_L12_T1_MRCC_13_P |

| 13 | Y8 | PL_IO_L12_T1_MRCC_13_N |

| 13 | Y6 | PL_IO_L13_T2_MRCC_13_P |

| 13 | Y5 | PL_IO_L13_T2_MRCC_13_N |

| 13 | AA7 | PL_IO_L14_T2_SRCC_13_P |

| 13 | AA6 | PL_IO_L14_T2_SRCC_13_N |

| 13 | AB2 | PL_IO_L15_T2_DQS_13_P |

| 13 | AB1 | PL_IO_L15_T2_DQS_13_N |

| 13 | AB5 | PL_IO_L16_T2_13_P |

| 13 | AB4 | PL_IO_L16_T2_13_N |

| 13 | AB7 | PL_IO_L17_T2_13_P |

| 13 | AB6 | PL_IO_L17_T2_13_N |

| 13 | Y4 | PL_IO_L18_T2_13_P |

| 13 | AA4 | PL_IO_L18_T2_13_N |

| 13 | R6 | PL_IO_L19_T3_13_P |

| 13 | T6 | PL_IO_L19_T3_13_N |

| 13 | T4 | PL_IO_L20_T3_13_P |

| 13 | U4 | PL_IO_L20_T3_13_N |

| 13 | V5 | PL_IO_L21_T3_DQS_13_P |

| 13 | V4 | PL_IO_L21_T3_DQS_13_N |

| 13 | U6 | PL_IO_L22_T3_13_P |

| 13 | U5 | PL_IO_L22_T3_13_N |

| 34 | J15 | PL_IO_L1_T0_34_P |

| 34 | K15 | PL_IO_L1_T0_34_N |

| 34 | J16 | PL_IO_L2_T0_34_P |

| 34 | J17 | PL_IO_L2_T0_34_N |

| 34 | L17 | PL_IO_L4_T0_34_P |

| 34 | M17 | PL_IO_L4_T0_34_N |

| 34 | N17 | PL_IO_L5_T0_34_P |

| 34 | N18 | PL_IO_L5_T0_34_N |

| 34 | J18 | PL_IO_L7_T1_34_P |

| 34 | K18 | PL_IO_L7_T1_34_N |

| 34 | J21 | PL_IO_L8_T1_34_P |

| 34 | J22 | PL_IO_L8_T1_34_N |

| 34 | J20 | PL_IO_L9_T1_DQS_34_P |

| 34 | K21 | PL_IO_L9_T1_DQS_34_N |

| 34 | L21 | PL_IO_L10_T1_34_P |

| 34 | L22 | PL_IO_L10_T1_34_N |

| 34 | K19 | PL_IO_L11_T1_SRCC_34_P |

| 34 | K20 | PL_IO_L11_T1_SRCC_34_N |

| 34 | L18 | PL_IO_L12_T1_MRCC_34_P |

| 34 | L19 | PL_IO_L12_T1_MRCC_34_N |

| 34 | N19 | PL_IO_L14_T2_SRCC_34_P |

| 34 | N20 | PL_IO_L14_T2_SRCC_34_N |

| 34 | M21 | PL_IO_L15_T2_DQS_34_P |

| 34 | M22 | PL_IO_L15_T2_DQS_34_N |

| 34 | N22 | PL_IO_L16_T2_34_P |

| 34 | P22 | PL_IO_L16_T2_34_N |

| 34 | R20 | PL_IO_L17_T2_34_P |

| 34 | R21 | PL_IO_L17_T2_34_N |

| 34 | P20 | PL_IO_L18_T2_34_P |

| 34 | P21 | PL_IO_L18_T2_34_N |

| 34 | P17 | PL_IO_L20_T3_34_P |

| 34 | P18 | PL_IO_L20_T3_34_N |

| 34 | T16 | PL_IO_L21_T3_DQS_34_P |

| 34 | T17 | PL_IO_L21_T3_DQS_34_N |

| 34 | R19 | PL_IO_L22_T3_34_P |

| 34 | T19 | PL_IO_L22_T3_34_N |

| 34 | R18 | PL_IO_L23_T3_34_P |

| 34 | T18 | PL_IO_L23_T3_34_N |

| 35 | H17 | PL_IO_0_35 |

| 35 | F16 | PL_IO_L1_T0_AD0_35_P |

| 35 | E16 | PL_IO_L1_T0_AD0_35_N |

| 35 | D16 | PL_IO_L2_T0_AD8_35_P |

| 35 | D17 | PL_IO_L2_T0_AD8_35_N |

| 35 | E15 | PL_IO_L3_T0_DQS_AD1_35_P |

| 35 | D15 | PL_IO_L3_T0_DQS_AD1_35_N |

| 35 | G15 | PL_IO_L4_T0_35_P |

| 35 | G16 | PL_IO_L4_T0_35_N |

| 35 | F18 | PL_IO_L5_T0_AD9_35_P |

| 35 | E18 | PL_IO_L5_T0_AD9_35_N |

| 35 | C15 | PL_IO_L7_T1_AD2_35_P |

| 35 | B15 | PL_IO_L7_T1_AD2_35_N |

| 35 | B16 | PL_IO_L8_T1_AD10_35_P |

| 35 | B17 | PL_IO_L8_T1_AD10_35_N |

| 35 | A16 | PL_IO_L9_T1_DQS_AD3_35_P |

| 35 | A17 | PL_IO_L9_T1_DQS_AD3_35_N |

| 35 | A18 | PL_IO_L10_T1_AD11_35_P |

| 35 | A19 | PL_IO_L10_T1_AD11_35_N |

| 35 | C17 | PL_IO_L11_T1_SRCC_35_P |

| 35 | C18 | PL_IO_L11_T1_SRCC_35_N |

| 35 | D18 | PL_IO_L12_T1_MRCC_35_P |

| 35 | C19 | PL_IO_L12_T1_MRCC_35_N |

| 35 | D20 | PL_IO_L14_T2_AD4_SRCC_35_P |

| 35 | C20 | PL_IO_L14_T2_AD4_SRCC_35_N |

| 35 | A21 | PL_IO_L15_T2_DQS_AD12_35_P |

| 35 | A22 | PL_IO_L15_T2_DQS_AD12_35_N |

| 35 | E21 | PL_IO_L17_T2_AD5_35_P |

| 35 | D21 | PL_IO_L17_T2_AD5_35_N |

| 35 | B21 | PL_IO_L18_T2_AD13_35_P |

| 35 | B22 | PL_IO_L18_T2_AD13_35_N |

| 35 | G19 | PL_IO_L20_T3_AD6_35_P |

| 35 | F19 | PL_IO_L20_T3_AD6_35_N |

| 35 | E19 | PL_IO_L21_T3_DQS_AD14_35_P |

| 35 | E20 | PL_IO_L21_T3_DQS_AD14_35_N |

| 35 | G20 | PL_IO_L22_T3_AD7_35_P |

| 35 | G21 | PL_IO_L22_T3_AD7_35_N |

| 35 | F21 | PL_IO_L23_T3_35_P |

| 35 | F22 | PL_IO_L23_T3_35_N |

| 35 | H22 | PL_IO_L24_T3_AD15_35_P |

| 35 | G22 | PL_IO_L24_T3_AD15_35_N |

| 35 | H18 | PL_IO_25_35 |

Technical Specifications

| Parameter * | Value | Unit |

|---|---|---|

| Basic Specifications | ||

| Number of GPIOs | 106 | |

| On-board oscillator frequency | 33.33 | MHz |

| On-board oscillator frequency (ASEM1-50.000MHZ-LC-T) | 50 | MHz |

| DDR3L Capacity | 4 | Gb |

| Quad SPI Flash Memory (MT25QL01GBBB8E12) | 1 | Gb |

| Power supply voltage (External) | 5, 3.3 | V |

| Internal Processor Core Voltage | 1.0 | V |

| Auxiliary supply voltage relative to GND | 1.8 | V |

| Output drivers supply voltage relative to GND | -0.5 to 3.6 | V |

| PS MIO I/O supply voltage (VCCO_MIO) | 1.8, 3.3 | V |

| PS MIO I/O input voltage | 1.8, 3.3 | V |

| PS DDR I/O input voltage | 1.35 or 1.5 | V |

| Maximum Processor Frequency | 667 | MHz |

* All parameters considered nominal. Numato Systems Pvt Ltd reserves the right to modify products without notice.

SODIMM PCB Edge Connector Pinout Map

| Signal | SODIMM Pin (Top) | SODIMM Pin (Bottom) | Signal |

|---|---|---|---|

| GND | 1 | 2 | GPHY_ATXRX_N |

| NC | 3 | 4 | GPHY_ATXRX_P |

| GND | 5 | 6 | GPHY_BTXRX_N |

| PL_IO_L18_T2_13_N | 7 | 8 | GPHY_BTXRX_P |

| PL_IO_L18_T2_13_P | 9 | 10 | P1_2 |

| GPHY_LINK_LED2 | 11 | 12 | GPHY_ACTIVITY_LED1 |

| GND | 13 | 14 | GPHY_CTXRX_N |

| GPHY_DTXRX_N | 15 | 16 | GPHY_CTXRX_P |

| GPHY_DTXRX_P | 17 | 18 | PL_IO_L11_T1_SRCC_13_N |

| PL_IO_L11_T1_SRCC_13_P | 19 | 20 | VCC_3V3 |

| PL_IO_L21_T3_DQS_13_P | 21 | 22 | PL_IO_L22_T3_13_P |

| PL_IO_L21_T3_DQS_13_N | 23 | 24 | PL_IO_L22_T3_13_N |

| NC | 25 | 26 | PL_IO_L14_T2_SRCC_13_P |

| GND | 27 | 28 | PL_IO_L14_T2_SRCC_13_N |

| PL_IO_L19_T3_13_P | 29 | 30 | PL_IO_L20_T3_13_P |

| PL_IO_L19_T3_13_N | 31 | 32 | VCC_3V3 |

| PL_IO_L20_T3_13_N | 33 | 34 | PL_IO_L1_T0_34_N |

| PL_IO_L2_T0_34_N | 35 | 36 | PL_IO_L1_T0_34_P |

| PL_IO_L2_T0_34_P | 37 | 38 | PL_IO_L7_T1_34_N |

| PL_IO_L7_T1_34_P | 39 | 40 | GND |

| GND | 41 | 42 | PL_IO_L20_T3_34_N |

| PL_IO_L4_T0_34_N | 43 | 44 | PL_IO_L20_T3_34_P |

| PL_IO_L4_T0_34_P | 45 | 46 | VCC_3V3 |

| P2_2 | 47 | 48 | PL_IO_L15_T2_DQS_13_N |

| NC | 49 | 50 | PL_IO_L15_T2_DQS_13_P |

| GND | 51 | 52 | PL_IO_L13_T2_MRCC_13_N |

| PL_IO_L12_T1_MRCC_13_N | 53 | 54 | PL_IO_L13_T2_MRCC_13_P |

| PL_IO_L12_T1_MRCC_13_P | 55 | 56 | PL_IO_L16_T2_13_N |

| PL_IO_L17_T2_13_N | 57 | 58 | PL_IO_L16_T2_13_P |

| PL_IO_L17_T2_13_P | 59 | 60 | VCC_3V3 |

| PL_IO_L21_T3_DQS_34_N | 61 | 62 | PL_IO_L23_T3_34_N |

| PL_IO_L21_T3_DQS_34_P | 63 | 64 | PL_IO_L23_T3_34_P |

| GND | 65 | 66 | PL_IO_L9_T1_DQS_34_N |

| PL_IO_L14_T2_SRCC_34_N | 67 | 68 | PL_IO_L9_T1_DQS_34_P |

| PL_IO_L14_T2_SRCC_34_P | 69 | 70 | PL_IO_L22_T3_34_P |

| P2_8 | 71 | 72 | VCC_3V3 |

| P2_7 | 73 | 74 | PL_IO_L22_T3_34_N |

| P1_7 | 75 | 76 | P2_5 |

| USB_OTG_ID | 77 | 78 | USB_PWR_EN |

| GND | 79 | 80 | PL_IO_L3P_T0_DQS_PUDC_B_34 |

| USB_OTG_DP | 81 | 82 | NC |

| USB_OTG_DN | 83 | 84 | PROGRAM B |

| NC | 85 | 86 | PL_IO_L16_T2_34_P |

| NC | 87 | 88 | VIN_3V3 |

| PL_IO_L16_T2_34_N | 89 | 90 | PL_IO_L12_T1_MRCC_34_P |

| P2_1 | 91 | 92 | PL_IO_L12_T1_MRCC_34_N |

| P1_4 | 93 | 94 | PL_IO_L15_T2_DQS_34_P |

| GND | 95 | 96 | PL_IO_L15_T2_DQS_34_N |

| PL_IO_L17_T2_34_P | 97 | 98 | PL_IO_L5_T0_34_P |

| PL_IO_L17_T2_34_N | 99 | 100 | PL_IO_L5_T0_34_N |

| PL_IO_L18_T2_34_P | 101 | 102 | PL_IO_L10_T1_34_P |

| PL_IO_L18_T2_34_N | 103 | 104 | PL_IO_L10_T1_34_N |

| GPIO48_PS_MIO48_501 | 105 | 106 | VCC_3V3 |

| SD0_DATA0(PS_MIO42_501) | 107 | 108 | SD0_CMD(PS_MIO41_501) |

| SD0_CLK(PS_MIO40_501) | 109 | 110 | P2_6 |

| SD0_DATA1(PS_MIO43_501) | 111 | 112 | SD0_DATA2(PS_MIO44_501) |

| GND | 113 | 114 | SD0_DATA3(PS_MIO45_501) |

| I2C0_SDA(PS_MIO47_501) | 115 | 116 | I2C0_SCL(PS_MIO46_501) |

| UART0_RX(PS_MIO50_501) | 117 | 118 | UART0_TX(PS_MIO51_501) |

| PL_IO_L11_T1_SRCC_34_N | 119 | 120 | PL_IO_L8_T1_34_N |

| PL_IO_L11_T1_SRCC_34_P | 121 | 122 | PL_IO_L8_T1_34_P |

| P1_8 | 123 | 124 | VCC_3V3 |

| PL_IO_L4_T0_35_P | 125 | 126 | PL_IO_L3_T0_DQS_AD1_35_P |

| NC | 127 | 128 | NC |

| NC | 129 | 130 | NC |

| GND | 131 | 132 | PL_IO_L1_T0_AD0_35_N |

| PL_IO_L4_T0_35_N | 133 | 134 | PL_IO_L7_T1_AD2_35_P |

| NC | 135 | 136 | PL_IO_L11_T1_SRCC_35_P |

| NC | 137 | 138 | PL_IO_L1_T0_AD0_35_P |

| PL_IO_L22_T3_AD7_35_P | 139 | 140 | PL_IO_L3_T0_DQS_AD1_35_N |

| NC | 141 | 142 | VCC_3V3 |

| PL_IO_L20_T3_AD6_35_N | 143 | 144 | PL_IO_L11_T1_SRCC_35_N |

| PL_IO_L20_T3_AD6_35_P | 145 | 146 | PL_IO_L5_T0_AD9_35_P |

| PL_IO_L5_T0_AD9_35_N | 147 | 148 | PL_IO_L24_T3_AD15_35_P |

| PL_IO_L24_T3_AD15_35_N | 149 | 150 | PL_IO_L12_T1_MRCC_35_P |

| GND | 151 | 152 | PL_IO_L14P_T2_AD4_SRCC_35_P |

| PL_IO_L8_T1_AD10_35_N | 153 | 154 | PL_IO_L8_T1_AD10_35_P |

| P1_3 | 155 | 156 | P2_3 |

| PL_IO_25_35 | 157 | 158 | PL_IO_L12_T1_MRCC_35_N |

| PL_IO_L14N_T2_AD4_SRCC_35_N | 159 | 160 | VCC_3V3 |

| P1_1 | 161 | 162 | PL_IO_L21_T3_DQS_AD14_35_P |

| PL_IO_L22_T3_AD7_35_N | 163 | 164 | PL_IO_L21_T3_DQS_AD14_35_N |

| PL_IO_L15_T2_DQS_AD12_35_N | 165 | 166 | PL_IO_L7_T1_AD2_35_N |

| P1_5 | 167 | 168 | P2_4 |

| GND | 169 | 170 | PL_IO_L2_T0_AD8_35_P |

| PL_IO_L15_T2_DQS_AD12_35_P | 171 | 172 | PL_IO_L2_T0_AD8_35_N |

| P1_6 | 173 | 174 | PL_IO_L17_T2_AD5_35_P |

| PL_IO_L18_T2_AD13_35_P | 175 | 176 | PL_IO_L23_T3_35_P |

| PL_IO_L10_T1_AD11_35_N | 177 | 178 | PL_IO_L23_T3_35_N |

| PL_IO_L18_T2_AD13_35_N | 179 | 180 | VCC_3V3 |

| PL_IO_L10_T1_AD11_35_P | 181 | 182 | NC |

| VRTC | 183 | 184 | SPI_DQ3 |

| GND | 185 | 186 | GND |

| n_RST_IN | 187 | 188 | NC |

| PL_IO_L17_T2_AD5_35_N | 189 | 190 | PL_IO_L9_T1_DQS_AD3_35_N |

| JTAG_TDO | 191 | 192 | VCC_3V3 |

| NC | 193 | 194 | PL_IO_0_35 |

| JTAG_TDI | 195 | 196 | PL_IO_L9_T1_DQS_AD3_35_P |

| JTAG_TCK | 197 | 198 | GND |

| JTAG_TMS | 199 | 200 | VDD5V |