Introduction

SI.No. SKU Description Operating temperature

1 NLFMPSD004 Neutron KU60 FPGA Development Board -40 to +100

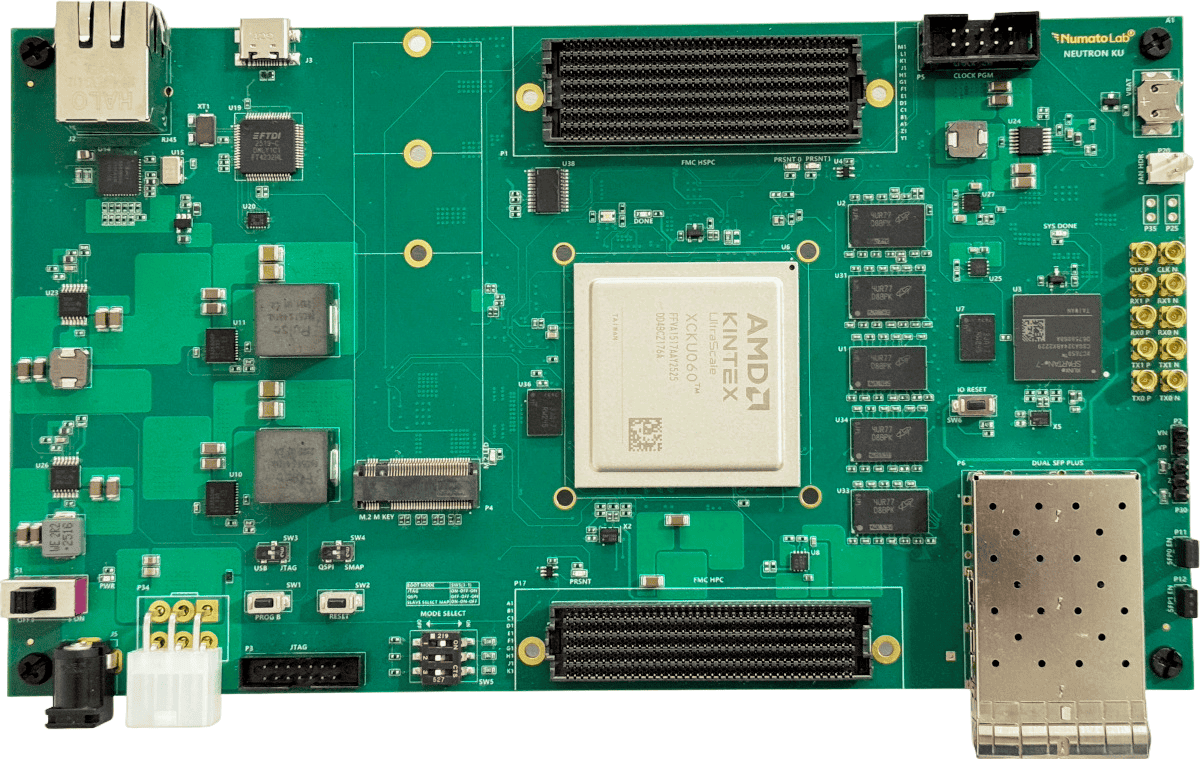

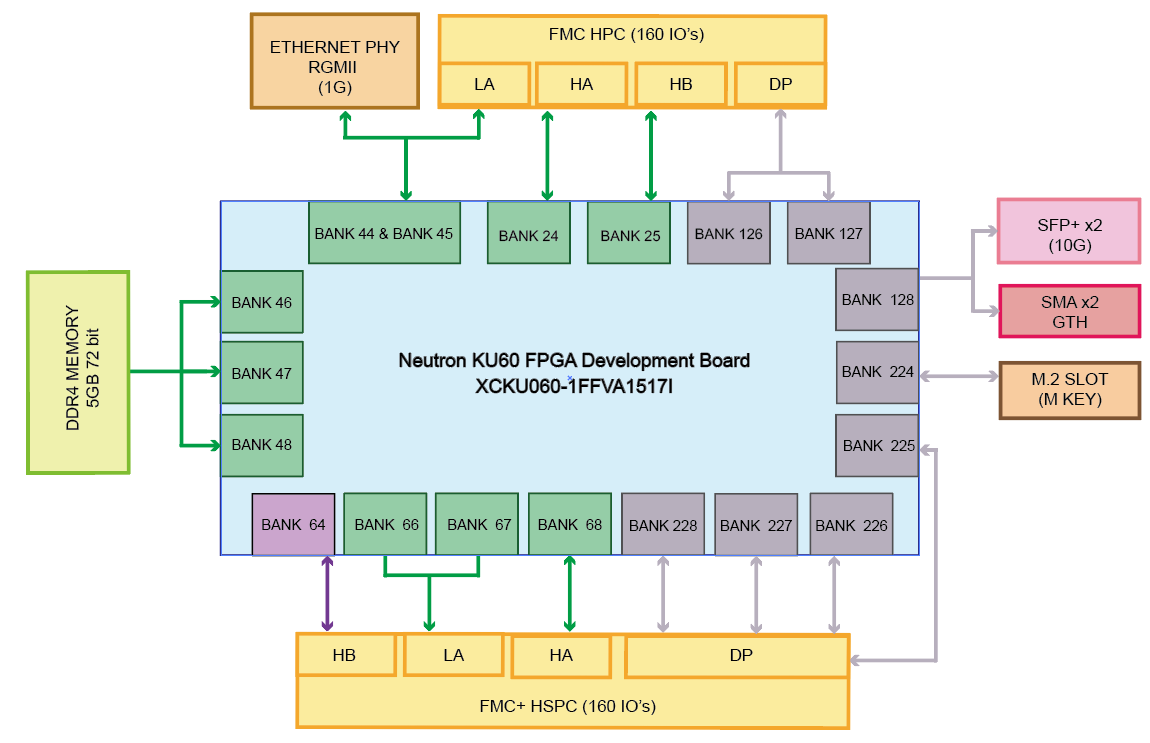

The Neutron KU60 FPGA Development Board is a high-performance platform built around the AMD Kintex UltraScale XCKU060 FPGA, designed for demanding high-speed computing, networking, and signal-processing applications. Featuring 5GB ECC-enabled DDR4, dual QSPI configuration memory, multiple clock sources, high-speed SFP+ connectivity, GTH transceiver access, and versatile expansion through FMC+ HSPC, FMC HPC, and an M.2 slot, the board delivers exceptional flexibility for advanced development. With JTAG/USB programming, and programmable clock options, Neutron KU60 provides a robust and adaptable environment for prototyping and deployment.

Board Features

- FPGA: AMD Kintex Ultrascale XCKU060-1FFVA1517I. Speed Grade -1.

- 5GB DDR4 SDRAM (72 Bit ECC) for reliable high-speed memory operation

- 512Mb (256 x 2) Dual QSPI flash for configuration

- Clocks:

- 1 × 300MHz CMOS for DDR4

- 1 × 200MHz CMOS for Fabric clock

- 1 × 200MHz CMOS for system clock

- 2 × SFP+ cages supporting high-speed serial networking

- 2-lane GTH transceiver access via SMA connectors

- M.2 slot (M-key) for NVMe or compatible modules

- 1 × Gigabit Ethernet port for network connectivity

- FMC+ HSPC connector (VITA 57.4) for high-bandwidth expansion

- FMC HPC connector (VITA 57.1) for additional I/O expansion

- FPGA Programming & Debugging via JTAG and USB.

- Programmable clock available for GTH reference and M.2 interface requirements

Application

- Data acquisition and processing

- Signal processing

- High-speed networking

- Embedded systems prototyping

- Scientific computing & research

How to use Neutron KU60 FPGA Development Board

The following sections describe in detail how to use this module.

Hardware Accessories Required

- 12V DC power supply (5A max current capacity).

- AMD Platform Cable USB II compatible JTAG programmer (optional).

- USB Type C cable.

- Neutron KU60 FPGA Development Board.

- FAN for FPGA

Connection Diagram

DC Power Supply

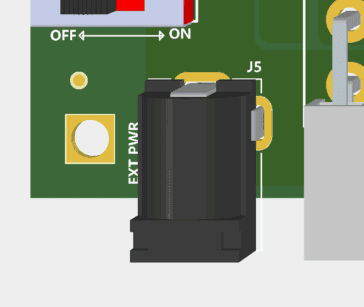

The board is configured to use power from DC power supply by connecting it to the External DC Jack. Please refer to the marking on the board for more details. The external power supply should be 12V, with sufficient current rating (5A max current capacity).

USB Interface

The onboard high speed USB controller helps a PC/Linux/Mac computer to communicate with this module. Use a USB C cable to connect with a PC.

PROG_B and Reset Button

PROGRAM_B

Neutron KU60 development board features a Push-button SW1 normally meant to be used as a “PROG_B” signal for configuration reset. Push-button SW1 is connected to FPGA pin AA9. For enabling ,manual configuration reset, push-button SW1 is connected to GND. The user can reconfigure the FPGA manually, by pressing this push-button SW1. “PROG_B” is an active-low input pin (pulled up with 4.7K external resistor) to the FPGA and it controls the configuration logic. When the PROG_B pin is de-asserted, resets the FPGA and initializes the new configuration.

Reset Button

Neutron KU60 development board features a Push-button SW2 normally meant to be used as a “Reset” signal for designs running on FPGA. Push-button SW2 is connected to FPGA pin AP13. Push-button SW2 is active-high. This pushbutton can also be used for any other input and is not just limited to be used as a Reset signal.

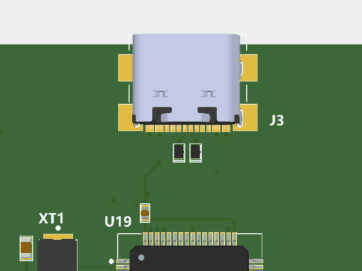

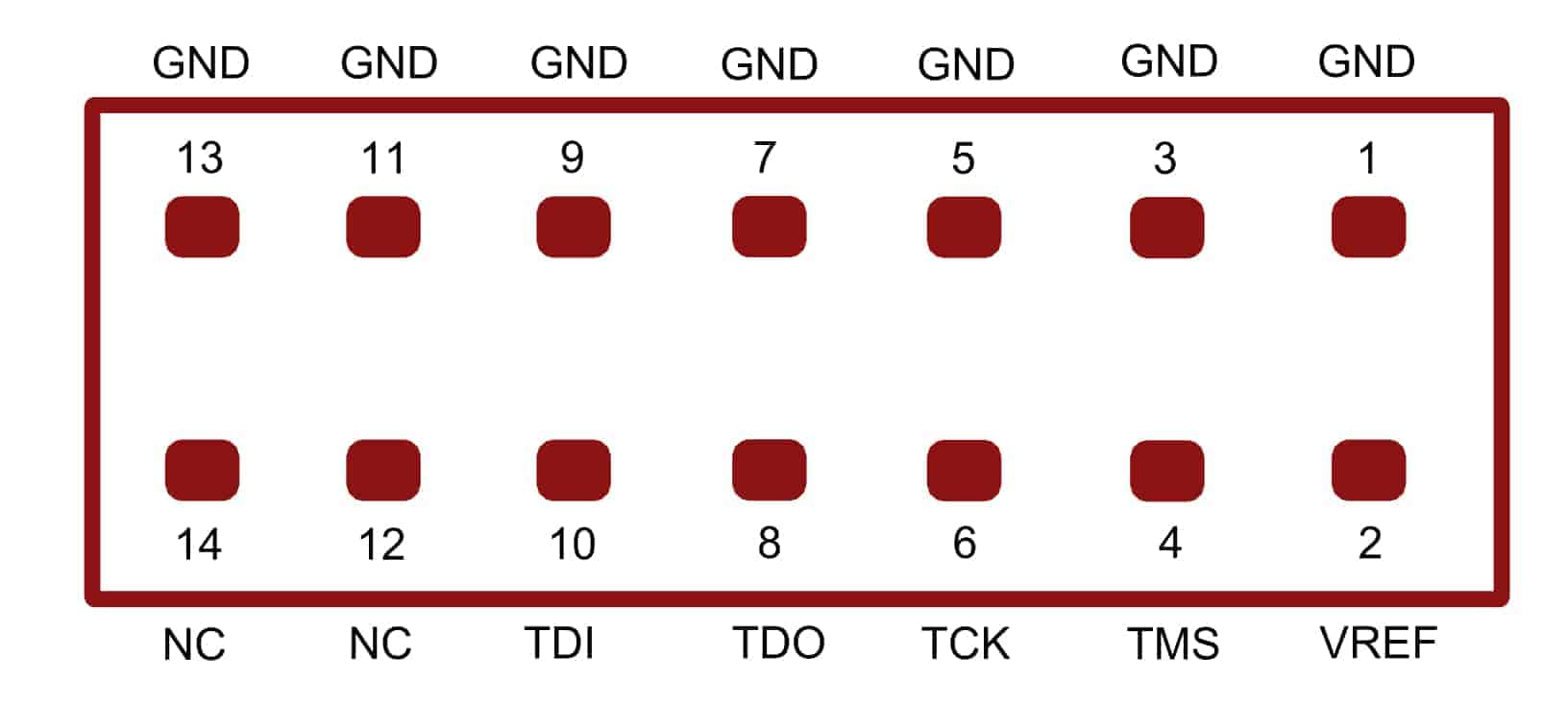

JTAG Connector

DDR4

The Neutron KU60 Development Module incorporates DDR4 SDRAM (MT40A512M16TD-062E), a high-speed, low-power memory device designed for high-bandwidth applications. The DDR4 architecture utilizes an 8n prefetch scheme with multiple internal memory banks, enabling efficient data access while supporting high I/O transfer rates with reduced operating voltage compared to previous DDR generations. The memory subsystem also implements Error Correction Code (ECC), which automatically detects and corrects single-bit errors and flags multi-bit errors during data transactions, significantly enhancing system reliability and data integrity for continuous and mission-critical FPGA applications.

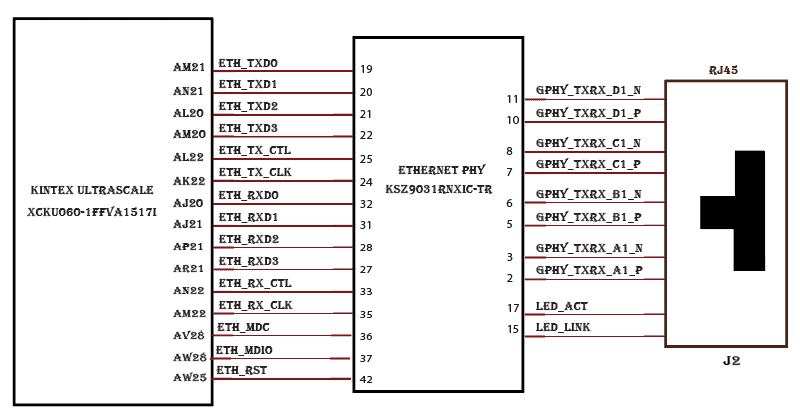

Gigabit Ethernet

The KSZ9031RNX is a completely integrated triple-speed (10BASE-T/100BASE-TX/1000BASE-T) Ethernet physical layer transceiver for transmission and reception of data. It provides the Reduced Gigabit Media Independent Interface (RGMII) for direct connection to RGMII MACs in Gigabit Ethernet processors and switches for data transfer at 10/100/1000 Mbps.

Quad SPI FLASH

The board includes two Quad SPI NOR flash memory devices (MT25QL256ABA8E12-0AAT), each with a capacity of 256 Mbit.

The flash memories operate at 3.3 V and are used for FPGA configuration storage and non-volatile data storage.

UART

The board uses an FTDI FT4232HL USB interface device.

Channel C of the FTDI is configured as a UART interface, and the associated signal connections are listed below.

Bank FPGA pin Signal name Function

65 AR12 IO_L9P_T1L_N4_AD12P_A14_D30_65 UART _TX

65 AT12 IO_L9N_T1L_N5_AD12N_A15_D31_65 UART _RX

SFP+ Cages

Neutron KU60 development board features two SFP+ cages (Small form-factor hot-pluggable optical module transceivers), which can be used for optical fiber communication.

SFP0

Bank FPGA Pin Signal Name Function

65 R34 MGTHTXP2_128 SFP0_TX_P

65 R35 MGTHTXN2_128 SFP0_TX_N

65 P36 MGTHRXP2_128 SFP0_RX_P

65 P37 MGTHRXN2_128 SFP0_RX_N

65 AP15 IO_L8P_T1L_N2_AD5P_A16_65 SFP0_TX_FLT

65 AW14 IO_L1N_T0L_N1_DBC_RS1_65 SFP0_TX_DSBL

65 AV14 IO_L1P_T0L_N0_DBC_RS0_65 SFP0_MOD_ABS

65 AR15 IO_L8N_T1L_N3_AD5N_A17_65 SFP0_RX_LOS

65 AV16 IO_L2P_T0L_N2_FOE_B_65 SFP0_RS0

65 AW15

IO_T0U_N12_A28_65 SFP0_RS1

SFP1

Bank FPGA pin Signal name Function

65 N34 MGTHTXP3_128 SFP1_TX_P

65 N35 MGTHTXN3_128 SFP1_TX_N

65 N38 MGTHRXP3_128 SFP1_RX_P

65 N39 MGTHRXN3_128 SFP1_RX_N

65 AP14 IO_L10P_T1U_N6_QBC_AD4P_A12_D28_65 SFP1_TX_FLT

65 AU15 IO_L4N_T0U_N7_DBC_AD7N_A25_65 SFP1_TX_DSBL

65 AT15 IO_L4P_T0U_N6_DBC_AD7P_A24_65 SFP1_MOD_ABS

65 AV12 IO_L5N_T0U_N9_AD14N_A23_65 SFP1_RX_LOS

65 AT13 IO_L7N_T1L_N1_QBC_AD13N_A19_65 SFP1_RS0

65 AT14 IO_L6P_T0U_N10_AD6P_A20_65 SFP1_RS1

Note: The I²C lines from the SFP connectors are routed through an onboard I²C multiplexer shared with other peripherals on the board. Please refer to the I²C Multiplexer section of this user manual for details.

SMA Connectors

The board provides SMA connectors connected directly to the FPGA’s high-speed GTH transceiver banks. SMA connectors are routed to two GTH transceiver data lanes, and a pair of SMA connector is routed to a GTH reference clock input.

These connectors allow the FPGA to interface with external high-speed serial data sources and sinks, as well as an external reference clock, for applications such as high-speed communication testing, protocol evaluation, and signal integrity measurements.

Bank FPGA Pin Signal Name Function

128 U34 MGTHTXP0_128 SMA_TX0_P

128 U35 MGTHTXN0_128 SMA_TX0_N

128 U38 MGTHRXP0_128 SMA_RX0_P

128 U39 MGTHRXN0_128 SMA_RX0_N

128 T36 MGTHTXP1_128 SMA_TX1_P

128 T37 MGTHTXN1_128 SMA_TX1_N

128 R38 MGTHRXP1_128 SMA_RX1_P

128 R39 MGTHRXN1_128 SMA_RX1_N

128 T32 MGTREFCLK0P_128 SMA_CLK0_P

128 T33 MGTREFCLK0N_128 SMA_CLK0_N

FMC HPC Header

Neutron KU60 FPGA development board features a high speed, high pin-count FMC connector which can be used to provide additional features and capabilities to it using custom or commercial-off-the-shelf daughter boards. Apart from IOs, 8 GTX lanes are available via FMC connector for custom purposes.

FMC HPC BANKS A TO E

A FMC Pin Name FPGA Pin B FMC Pin Name FPGA Pin C FMC Pin Name FPGA Pin D FMC Pin Name FPGA Pin E FMC Pin Name FPGA Pin

A1 GND B1 GND C1 GND D1 HPC_PG_C2M E1 GND

A2 HPC_DP1_M2C_P AA38 B2 GND C2 HPC_DP0_C2M_P AC34 D2 GND E2 HPC_HA01_CC_P AU32

A3 HPC_DP1_M2C_N AA39 B3 GND C3 HPC_DP0_C2M_N AC35 D3 GND E3 HPC_HA01_CC_N AV32V

A4 GND B4 NC C4 GND D4 HPC_GBTCLK0_M2C_P AD32 E4 GND

A5 GND B5 NC C5 GND D5 HPC_GBTCLK0_M2C_N AD33 E5 GND

A6 HPC_DP2_M2C_P W38 B6 GND C6 HPC_DP0_M2C_P AB36 D6 GND E6 HPC_HA05_P AP30

A7 HPC_DP2_M2C_N W39 B7 GND C7 HPC_DP0_M2C_N AB37 D7 GND E7 HPC_HA05_N AP31

A8 GND B8 NC C8 GND D8 HPC_LA01_CC_P AU21 E8 GND

A9 GND B9 NC C9 GND D9 HPC_LA01_CC_N AV22 E9 HPC_HA09_P AM32

A10 HPC_DP3_M2C_P V36 B10 GND C10 HPC_LA06_P AK23 D10 GND E10 HPC_HA09_N AN32

A11 HPC_DP3_M2C_N V37 B11 GND C11 HPC_LA06_N AL23 D11 HPC_LA05_P AE20 E11 GND

A12 GND B12 HPC_DP7_M2C_P AC38 C12 GND D12 HPC_LA05_N AE21 E12 HPC_HA13_P AK32

A13 GND B13 HPC_DP7_M2C_N AC39 C13 GND D13 GND E13 HPC_HA13_N AL32

A14 HPC_DP4_M2C_P AG38 B14 GND C14 HPC_LA10_P AE23 D14 HPC_LA09_P AG21 E14 GND

A15 HPC_DP4_M2C_N AG39 B15 GND C15 HPC_LA10_N AF23 D15 HPC_LA09_N AG22 E15 HPC_HA16_P AH31

A16 GND B16 HPC_DP6_M2C_P AE38 C16 GND D16 GND E16 HPC_HA16_N AH32

A17 GND B17 HPC_DP6_M2C_N AE39 C17 GND D17 HPC_LA13_P AE22 E17 GND

A18 HPC_DP5_M2C_P AF36 B18 GND C18 HPC_LA14_P AD20 D18 HPC_LA13_N AF22 E18 HPC_HA20_P AF29

A19 HPC_DP5_M2C_N AF37 B19 GND C19 HPC_LA14_N AD21 D19 GND E19 HPC_HA20_N AG29

A20 GND B20 HPC_GBTCLK1_M2C_P AB32 C20 GND D20 HPC_LA17_CC_P AR26 E20 GND

A21 GND B21 HPC_GBTCLK1_M2C_N AB33 C21 GND D21 HPC_LA17_CC_N AR27 E21 HPC_HB03_P AW30

A22 HPC_DP1_C2M_P AA34 B22 GND C22 HPC_LA18_CC_P AL27 D22 GND E22 HPC_HB03_P AW31

A23 HPC_DP1_C2M_N AA35 B23 GND C23 HPC_LA18_CC_N AL28 D23 HPC_LA23_P AV26 E23 GND

A24 GND B24 NC C24 GND D24 HPC_LA23_N AV27 E24 HPC_HB05_P AP30

A25 GND B25 NC C25 GND D25 GND E25 HPC_HB05_N AP31

A26 HPC_DP2_C2M_P Y36 B26 GND C26 HPC_LA27_P AR28 D26 HPC_LA26_P AN28 E26 GND

A27 HPC_DP2_C2M_N Y37 B27 GND C27 HPC_LA27_N AT28 D27 HPC_LA26_N AP28 E27 HPC_HB09_P AM32

A28 GND B28 NC C28 GND D28 GND E28 HPC_HB09_N AN32

A29 GND B29 NC C29 GND D29 FPGA_TCK AA11 E29 GND

A30 HPC_DP3_C2M_P W34 B30 GND C30 NC AE12 D30 HSPC_TDO_HPC_TDI E30 HPC_HB13_P AK32

A31 HPC_DP3_C2M_N W35 B31 GND C31 NC AF12 D31 HPC_TDO_SYS_TDI E31 HPC_HB13_N AL32

A32 GND B32 HPC_DP7_C2M_P AD36 C32 GND D32 3V3AUX E32 GND

A33 GND B33 HPC_DP7_C2M_N AD37 C33 GND D33 FPGA_TMS W11 E33 HPC_HB19_P AE28

A34 HPC_DP4_C2M_P AH36 B34 GND C34 GND D34 NC E34 HPC_HB19_N AF28

A35 HPC_DP4_C2M_N AH37 B35 GND C35 P12V0 D35 GND E35 GND

A36 GND B36 HPC_DP6_C2M_P AE34 C36 GND D36 P3V3 E36 HPC_HB21_P AH28

A37 GND B37 HPC_DP6_C2M_N AE35 C37 P12V0 D37 GND E37 HPC_HB21_N AJ28

A38 HPC_DP5_C2M_P AG34 B38 GND C38 GND D38 P3V3 E38 GND

A39 HPC_DP5_C2M_N AG35 B39 GND C39 P3V3 D39 GND E39 VCCIO_1V8

A40 GND B40 NC C40 GND D40 P3V3 E40 GND

FMC HPC BANKS F TO K

F FMC Pin Name FPGA Pin G FMC Pin Name FPGA Pin H FMC Pin Name FPGA Pin J FMC Pin Name FPGA Pin K FMC Pin Name FPGA Pin

F1 HPC_PG_M2C G1 GND H1 NC J1 GND K1 NC

F2 GND G2 HPC_CLK1_M2C_P AM26 H2 HPC_PRSNT_M2C_L J2 HPC_CLK3_BIDIR_P AM27 K2 GND

F3 GND G3 HPC_CLK1_M2C_N AN26 H3 GND J3 HPC_CLK3_BIDIR_N AN27

K3 GND

F4 HPC_HA00_CC_P AP29 G4 GND H4 HPC_CLK0_M2C_P AV24 J4 GND K4 HPC_CLK2_BIDIR_P AP25

F5 HPC_HA00_CC_N AR30 G5 GND H5 HPC_CLK0_M2C_N AW24

J5 GND K5 HPC_CLK2_BIDIR_N AR25

F6 GND G6 HPC_LA00_CC_P AN24 H6 GND J6 HPC_HA03_P AW30 K6 GND

F7 HPC_HA04_P AN33 G7 HPC_LA00_CC_N AP24 H7 HPC_LA02_P AT22 J7 HPC_HA03_N AW31 K7 HPC_HA02_P AU29

F8 HPC_HA04_N AP33 G8 GND H8 HPC_LA02_N AU22 J8 GND K8 HPC_HA02_N AU30

F9 GND G9 HPC_LA03_P AV21 H9 GND J9 HPC_HA07_P AV29 K9 GND

F10 HPC_HA08_P AL30 G10 HPC_LA03_N AW21 H10 HPC_LA04_P AR22 J10 HPC_HA07_N AW29 K10 HPC_HA06_P AT29

F11 HPC_HA08_N AM30 G11 GND H11 HPC_LA04_N AR23 J11 GND K11 HPC_HA06_N AT30

F12 GND G12 HPC_LA08_P AV23 H12 GND J12 HPC_HA11_P AU31 K12 GND

F13 HPC_HA12_P AJ33 G13 HPC_LA08_N AW23 H13 HPC_LA07_P AN23 J13 HPC_HA11_N AV31 K13 HPC_HA10_P AR31

F14 HPC_HA12_N AK33 G14 GND H14 HPC_LA07_N AR23 J14 GND K14 HPC_HA10_N AR32

F15 GND G15 HPC_LA12_P AT23 H15 GND J15 HPC_HA14_P AE30 K15 GND

F16 HPC_HA15_P AJ31 G16 HPC_LA12_N AT24 H16 HPC_LA11_P AK20 J16 HPC_HA14_N AF30 K16 HPC_HA17_CC_P AL29

F17 HPC_HA15_N AK31 G17 GND H17 HPC_LA11_N AK21 J17 GND K17 HPC_HA17_CC_N AM29

F18 GND G18 HPC_LA16_P AH22 H18 GND J18 HPC_HA18_P AH29 K18 GND

F19 HPC_HA19_P AE28 G19 HPC_LA16_N AH23 H19 HPC_LA15_P AF20 J19 HPC_HA18_N AJ29 K19 HPC_HA21_P AH28

F20 HPC_HA19_N AF28 G20 GND H20 HPC_LA15_N AG20 J20 GND K20 HPC_HA21_N AJ28

F21 GND G21 HPC_LA20_P AL24 H21 GND J21 HPC_HA22_P AJ30 K21 GND

F22 HPC_HB02_P AU29 G22 HPC_LA20_N AL25 H22 HPC_LA19_P AM24 J22 HPC_HA22_N AK30 K22 HPC_HA23_P AM31

F23 HPC_HB02_N AU30 G23 GND H23 HPC_LA19_N AM25 J23 GND K23 HPC_HA23_N AN31

F24 GND G24 HPC_LA22_P AJ25 H24 GND J24 HPC_HB01_P AT35 K24 GND

F25 HPC_HB04_P AN33 G25 HPC_LA22_N AK25 H25 HPC_LA21_P AH24 J25 HPC_HB01_N AU35 K25 HPC_HB00_CC_P AW33

F26 HPC_HB04_N AP33 G26 GND H26 HPC_LA21_N AJ24 J26 GND K26 HPC_HB00_CC_N AW34

F27 GND G27 HPC_LA25_P AF25 H27 GND J27 HPC_HB07_P AV38 K27 GND

F28 HPC_HB08_P AL30 G28 HPC_LA25_N AG25 H28 HPC_LA24_P AK27 J28 HPC_HB07_N AV39 K28 HPC_HB06_CC_P AW35

F29 HPC_HB08_N AM30 G29 GND H29 HPC_LA24_N AK28 J29 GND K29 HPC_HB06_CC_N AW36

F30 GND G30 HPC_LA29_P AH26 H30 GND J30 HPC_HB11_P AV33 K30 GND

F31 HPC_HB12_P AJ33 G31 HPC_LA29_N

AJ26 H31 HPC_LA28_P AE27 J31 HPC_HB11_N AV34 K31 HPC_HB10_P AT34

F32 HPC_HB12_N AK33 G32 GND H32 HPC_LA28_N AF27 J32 GND K32 HPC_HB10_N AU34

F33 GND G33 HPC_LA31_P AD26 H33 GND J33 HPC_HB15_P AL39 K33 GND

F34 HPC_HB16_P AH31 G34 HPC_LA31_N AE26 H34 HPC_LA30_P AD25 J34 HPC_HB15_N AM39 K34 HPC_HB14_P AN38

F35 HPC_HB16_N AH32 G35 GND H35 HPC_LA30_N AE25 J35 GND K35 HPC_HB14_N AP38

F36 GND G36 NC H36 GND J36 HPC_HB18_P AM34 K36 GND

F37 HPC_HB20_P AF29 G37 NC H37 HPC_LA32_P AF24 J37 HPC_HB18_N AM35 K37 HPC_HB17_CC_P AM36

F38 HPC_HB20_N AG29 G38 GND H38 HPC_LA32_N AG24 J38 GND K38 HPC_HB17_CC_N AM37

F39 GND G39 VADJ H39 GND J39 HPC_VIO_B_M2C K39 GND

F40 VADJ G40 GND H40 VADJ J40 GND K40 HPC_VIO_B_M2C

FMC+ HSPC Header

Neutron KU60 development board features a FMC+ HSPC (High serial pin count) connector on the board that follows the ANSI/VITA 57.4 specification and provides a high-pin-count interface for FMC+ mezzanine cards.

The connector supports 16 FPGA GTH transceiver lane pairs, along with fabric-based differential I/O, enabling high-speed serial and parallel expansion through FMC+ modules.

FMC+ HSPC BANKS A TO E

A FMC Pin Name FPGA Pin B FMC Pin Name FPGA Pin C FMC Pin Name FPGA Pin D FMC Pin Name FPGA Pin E FMC Pin Name FPGA Pin

A1 GND B1 GND C1 GND D1 HSPC_PG_C2M E1 GND

A2 HSPC_DP1_M2C_P AK2 B2 GND C2 HSPC_DP0_C2M_P AL8 D2 GND E2 HSPC_HA01_CC_P C22

A3 HSPC_DP1_M2C_N AK1 B3 GND C3 HSPC_DP0_C2M_N AL7 D3 GND E3 HSPC_HA01_CC_N B22

A4 GND B4 HSPC_DP9_M2C_P AF2 C4 GND D4 HSPC_GBTCLK0_M2C_P AH10 E4 GND

A5 GND B5 HSPC_DP9_M2C_N AF1 C5 GND D5 HSPC_GBTCLK0_M2C_N AH9 E5 GND

A6 HSPC_DP2_M2C_P AJ4 B6 GND C6 HSPC_DP0_M2C_P AL4 D6 GND E6 HSPC_HA05_P J23

A7 HSPC_DP2_M2C_N AJ3 B7 GND C7 HSPC_DP0_M2C_N AL3 D7 GND E7 HSPC_HA05_N J24

A8 GND B8 HSPC_DP8_M2C_P AG4 C8 GND D8 HSPC_LA01_CC_P A13 E8 GND

A9 GND B9 HSPC_DP8_M2C_N AG3 C9 GND D9 HSPC_LA01_CC_N A12 E9 HSPC_HA09_P K21

A10 HSPC_DP3_M2C_P AH2 B10 GND C10 HSPC_LA06_P C12 D10 GND E10 HSPC_HA09_N J21

A11 HSPC_DP3_M2C_N AH1 B11 GND C11 HSPC_LA06_N B12 D11 HSPC_LA05_P E13 E11 GND

A12 GND B12 HSPC_DP7_M2C_P AM2 C12 GND D12 HSPC_LA05_N E12 E12 HSPC_HA13_P L23

A13 GND B13 HSPC_DP7_M2C_N AM1 C13 GND D13 GND E13 HSPC_HA13_N L24

A14 HSPC_DP4_M2C_P AR4 B14 GND C14 HSPC_LA10_P K13 D14 HSPC_LA09_P J13 E14 GND

A15 HSPC_DP4_M2C_N AR3 B15 GND C15 HSPC_LA10_N K12 D15 HSPC_LA09_N H13 E15 HSPC_HA16_P M20

A16 GND B16 HSPC_DP6_M2C_P AN4 C16 GND D16 GND E16 HSPC_HA16_N M21

A17 GND B17 HSPC_DP6_M2C_N AN3 C17 GND D17 HSPC_LA13_P K15 E17 GND

A18 HSPC_DP5_M2C_P AP2 B18 GND C18 HSPC_LA14_P P15 D18 HSPCLA13_N J15 E18 HSPC_HA20_P R21

A19 HSPC_DP5_M2C_N AP1 B19 GND C19 HSPC_LA14_N P14 D19 GND E19 HSPC_HA20_N P21

A20 GND B20 HSPC_GBTCLK1_M2C_P AH10 C20 GND D20 HSPC_LA17_CC_P C17 E20 GND

A21 GND B21 HSPC_GBTCLK1_M2C_N AH9 C21 GND D21 HSPC_LA17_CC_N B17 E21 HSPC_HB03_P E21

A22 HSPC_DP1_C2M_P AK6 B22 GND C22 HSPC_LA18_CC_P F17 D22 GND E22 HSPC_HB03_N E22

A23 HSPC_DP1_C2M_N AK5 B23 GND C23 HSPC_LA18_CC_N E17 D23 HSPC_LA23_P F18 E23 GND

A24 GND B24 HSPC_DP9_C2M_P AF6 C24 GND D24 HSPC_LA23_N E18 E24 HSPC_HB05_P J23

A25 GND B25 HSPC_DP9_C2M_N AF5 C25 GND D25 GND E25 HSPC_HB05_N J24

A26 HSPC_DP2_C2M_P AJ8 B26 GND C26 HSPC_LA27_P H18 D26 HSPC_LA26_P K16 E26 GND

A27 HSPC_DP2_C2M_N AJ7 B27 GND C27 HSPC_LA27_N H17 D27 HSPC_LA26_N J16 E27 HSPC_HB09_P K21

A28 GND B28 HSPC_DP8_C2M_P AG8 C28 GND D28 GND E28 HSPC_HB09_N J21

A29 GND B29 HSPC_DP8_C2M_N AG7 C29 GND D29 FPGA_TCK AA11 E29 GND

A30 HSPC_DP3_C2M_P AH6 B30 GND C30 NC AE12 D30 FPGA_TDO_HSPC_TDI T10 E30 HSPC_HB13_P L23

A31 HSPC_DP3_C2M_N AH5 B31 GND C31 NC AF12 D31 HSPC_TDO_HPC_TDI E31 HSPC_HB13_N L24

A32 GND B32 HSPC_DP7_C2M_P AM6 C32 GND D32 3V3AUX E32 GND

A33 GND B33 HSPC_DP7_C2M_N AM5 C33 GND D33 FPGA_TMS W11 E33 HSPC_HB19_P R20

A34 HSPC_DP4_C2M_P AR8 B34 GND C34 GND D34 NC E34 HSPC_HB19_N P20

A35 HSPC_DP4_C2M_N AR7 B35 GND C35 P12V0 D35 P3V3 E35 GND

A36 GND B36 HSPC_DP6_C2M_P AN8 C36 GND D36 P3V3 E36 HSPC_HB21_P G24

A37 GND B37 HSPC_DP6_C2M_N AN7 C37 P12V0 D37 GND E37 HSPC_HB21_N F24

A38 HSPC_DP5_C2M_P AP6 B38 GND C38 GND D38 P3V3 E38 GND

A39 HSPC_DP5_C2M_N AP5 B39 GND C39 P3V3 D39 GND E39 VCCIO_18

A40 GND B40 NC C40 GND D40 P3V3 E40 GND

FMC+ HSPC BANKS F TO K

F FMC Pin Name FPGA Pin G FMC Pin Name FPGA Pin H FMC Pin Name FPGA Pin J FMC Pin Name FPGA Pin K FMC Pin Name FPGA Pin

F1 HSPC_PG_M2C G1 GND H1 NC J1 GND K1 NC

F2 GND G2 HSPC_CLK1_M2C_P J20 H2 PRSNT_M2C_L J2 HSPC_CLK3_BIDIR_P K18 K2 GND

F3 GND G3 HSPC_CLK1_M2C_N J19 H3 GND J3 HSPC_CLK3_BIDIR_N

J18K3 GND

F4 HSPC_HA00_CC_P H21 G4 GND H4 HSPC_CLK0_M2C_P G16 J4 GND K4 HSPC_CLK2_BIDIR_P J14

F5 HSPC_HA00_CC_N H22 G5 GND H5 HSPC_CLK0_M2C_N G15 J5 GND K5 HSPC_CLK2_BIDIR_N H14

F6 GND G6 HSPC_LA00_CC_P F15 H6 GND J6 HSPC_HA03_P E21 K6 GND

F7 HSPC_HA04_P G21 G7 HSPC_LA00_CC_N E15 H7 HSPC_LA02_P D15 J7 HSPC_HA03_N E22 K7 HSPC_HA02_P D21

F8 HSPC_HA04_N G22 G8 GND H8 HSPC_LA02_N D14 J8 GND K8 HSPC_HA02_N C21

F9 GND G9 HSPC_LA03_P E16 H9 GND J9 HSPC_HA07_P B21 K9 GND

F10 HSPC_HA08_P K22 G10 HSPC_LA03_N D16 H10 HSPC_LA04_P A15 J10 HSPC_HA07_N A22 K10 HSPC_HA06_P B24

F11 HSPC_HA08_N K23 G11 GND H11 HSPC_LA04_N A14 J11 GND K11 HSPC_HA06_N A24

F12 GND G12 HSPC_LA08_P C14 H12 GND J12 HSPC_HA11_P T22 K12 GND

F13 HSPC_HA12_P L20 G13 HSPC_LA08_N B14 H13 HSPC_LA07_P D13 J13 HSPC_HA11_N R22 K13 HSPC_HA10_P D23

F14 HSPC_HA12_N K20 G14 GND H14 HSPC_LA07_N C13 J14 GND K14 HSPC_HA10_N C23

F15 GND G15 HSPC_LA12_P F13 H15 GND J15 HSPC_HA14_P T23 K15 GND

F16 HSPC_HA15_P N21 G16 HSPC_LA12_N F12 H16 HSPC_LA11_P B16 J16 HSPC_HA14_N R23 K16 HSPC_HA17_CC_P D24

F17 HSPC_HA15_N N22 G17 GND H17 HSPC_LA11_N B15 J17 GND K17 HSPC_HA17_CC_N C24

F18 GND G18 HSPC_LA16_P L13 H18 GND J18 HSPC_HA18_P F23 K18 GND

F19 HSPC_HA19_P R20 G19 HSPC_LA16_N L12 H19 HSPC_LA15_P G14 J19 HSPC_HA18_N E23 K19 HSPC_HA21_P G24

F20 HSPC_HA19_N P20 G20 GND H20 HSPC_LA15_N F14 J20 GND K20 HSPC_HA21_N F24

F21 GND G21 HSPC_LA20_P A18 H21 GND J21 HSPC_HA22_P P23 K21 GND

F22 HSPC_HB02_P D21 G22 HSPC_LA20_N A17 H22 HSPC_LA19_P B19 J22 HSPC_HA22_N N23 K22 HSPC_HA23_P H23

F23 HSPC_HB02_N C21 G23 GND H23 HSPC_LA19_N A19 J23 GND K23 HSPC_HA23_N H24

F24 GND G24 HSPC_LA22_P D19 H24 GND J24 HSPC_HB01_P AG17 K24 GND

F25 HSPC_HB04_P G21 G25 HSPC_LA22_N C19 H25 HSPC_LA21_P B20 J25 HSPC_HB01_N AG16 K25 HSPC_HB00_CC_P AN18

F26 HSPC_HB04_N G22 G26 GND H26 HSPC_LA21_N A20 J26 GND K26 HSPC_HB00_CC_N AN17

F27 GND G27 HSPC_LA25_P M17 H27 GND J27 HSPC_HB07_P AJ16 K27 GND

F28 HSPC_HB08_P K22 G28 HSPC_LA25_N M16 H28 HSPC_LA24_P L17 J28 HSPC_HB07_N AK16 K28 HSPC_HB06_CC_P AE18

F29 HSPC_HB08_N K23 G29 GND H29 HSPC_LA24_N K17 J29 GND K29 HSPC_HB06_CC_N AF18

F30 GND G30 HSPC_LA29_P D18 H30 GND J30 HSPC_HB11_P AF19 K30 GND

F31 HSPC_HB12_P L20 G31 HSPC_LA29_N

C18 H31 HSPC_LA28_P F20 J31 HSPC_HB11_N AG19 K31 HSPC_HB10_P AK18

F32 HSPC_HB12_N K20 G32 GND H32 HSPC_LA28_N E20 J32 GND K32 HSPC_HB10_N AK17

F33 GND G33 HSPC_LA31_P G20 H33 GND J33 HSPC_HB15_P AL19 K33 GND

F34 HSPC_HB16_P M20 G34 HSPC_LA31_N F19 H34 HSPC_LA30_P L19 J34 HSPC_HB15_N AL18 K34 HSPC_HB14_P AM19

F35 HSPC_HB16_N M21 G35 GND H35 HSPC_LA30_N L18 J35 GND K35 HSPC_HB14_N AN19

F36 GND G36 HSPC_LA33_P R18 H36 GND J36 HSPC_HB18_P AT19 K36 GND

F37 HSPC_HB20_P R21 G37 HSPC_LA33_N R17 H37 HSPC_LA32_P H19 J37 HSPC_HB18_N AU19 K37 HSPC_HB17_CC_P AR18

F38 HSPC_HB20_N P21 G38 GND H38 HSPC_LA32_N G19 J38 GND K38 HSPC_HB17_CC_N AR17

F39 GND G39 VCCIO_1V8 H39 GND J39 HSPC_VIO_B_M2C K39 GND

F40 VCCIO_1V8 G40 GND H40 VCCIO_1V8 J40 GND K40 HSPC_VIO_B_M2C

FMC+ HSPC L , M, Z & Y

L FMC Pin Name FPGA Pin M FMC Pin Name FPGA Pin Z FMC Pin Name FPGA Pin Y FMC Pin Name FPGA Pin

L1

NC M1 GND Z1 HSPC_PRSNT_M2C_L Y1 GND

L2 GND M2 NC Z2 GND Y2 NC

L3 GND M3 NC Z3 GND Y3 NC

L4 NC M4 GND Z4 NC Y4 GND

L5 NC M5 GND Z5 NC Y5 GND

L6 GND M6 NC Z6 GND Y6 NC

L7 GND M7 NC Z7 GND Y7 NC

L8 HSPC_GBTCLK3_M2C_P AA8 M8 GND Z8 NC Y8 GND

L9 HSPC_GBTCLK3_M2C_N AA7 M9 GND Z9 CN Y9 GND

L10 GND M10 NC Z10 GND Y10 HSPC_DP10_M2C_P AD2

L11 GND M11 NC Z11 GND Y11 HSPC_DP10_M2C_N AD1

L12 HSPC_GBTCLK2_M2C_P AE8 M12 GND Z12 HSPC_DP11_M2C_P AC4 Y12 GND

L13 HSPC_GBTCLK2_M2C_N AE7 M13 GND Z13 HSPC_DP11_M2C_N AC3 Y13 GND

L14 GND M14 NC Z14 GND Y14 HSPC_DP12_M2C_P AB2

L15 GND M15 NC Z15 GND Y15 HSPC_DP12_M2C_N AB1

L16 HSPC_SYNC_C2M_P P19 M16 GND Z16 HSPC_DP13_M2C_P Y2 Y16 GND

L17 HSPC_SYNC_C2M_N P18 M17 GND Z17 HSPC_DP13_M2C_N Y1 Y17 GND

L18 GND M18 HSPC_DP14_C2M_P Y6 Z18 GND Y18 HSPC_DP14_M2C_P W4

L19 GND M19 HSPC_DP14_C2M_N Y5 Z19 GND Y19 HSPC_DP14_M2C_N W3

L20 HSPC_REFCLK_C2M_P T18 M20 GND Z20 NC Y20 GND

L21 HSPC_REFCLK_C2M_N T17 M21 GND Z21 NC Y21 GND

L22 GND M22 HSPC_DP15_C2M_P V6 Z22 GND Y22 HSPC_DP15_M2C_P V2

L23 GND M23 HSPC_DP15_C2M_N V5 Z23 GND Y23 HSPC_DP15_M2C_N V1

L24 HSPC_REFCLK_M2C_P P13 M24 GND Z24 HSPC_DP10_C2M_P AE4 Y24 GND

L25 HSPC_REFCLK_M2C_N N13 M25 GND Z25 HSPC_DP10_C2M_N AE3 Y25 GND

L26 GND M26 NC Z26 GND Y26 HSPC_DP11_C2M_P AD6

L27 GND M27 NC Z27 GND Y27 HSPC_DP11_C2M_N AD6

L28 HSPC_SYNC_M2C_P N12 M28 GND Z28 HSPC_DP12_C2M_P AB6 Y28 GND

L29 HSPC_SYNC_M2C_N M12 M29 GND Z29 HSPC_DP12_C2M_P AB5 Y29 GND

L30 GND M30 NC Z30 GND Y30 HSPC_DP13_C2M_P AA4

L31 GND M31 NC Z31 GND Y31 HSPC_DP13_C2M_N AA3

L32 NC M32 GND Z32 NC Y32 GND

L33 NC M33 GND Z33 NC Y33 GND

L34 GND M34 NC Z34 GND Y34 NC

L35 GND M35 NC Z35 GND Y35 NC

L36 P12V0 M36 GND Z36 NC Y36 GND

L37 P12V0 M37 GND Z37 NC Y37 GND

L38 GND M38 NC Z38 GND Y38 NC

L39 GND M39 NC Z39 GND Y39 NC

L40 P12V0 M40 GND Z40 P3V3 Y40 GND

M.2 Edge Connector

The Neutron board includes an M.2 M key slot that supports PCI Express–based expansion modules, such as NVMe solid-state drives (SSDs).

The connector is interfaced directly to the FPGA, enabling high-speed storage and custom PCIe-based applications.

Bank FPGA Pin Signal Name Function

224 AW8 MGTHTXP0_224 M2_TX0_P

224 AW7 MGTHTXN0_224 M2_TX0_N

224 AW4 MGTHRXP0_224 M.2_RX0_P

224 AW3 MGTHRXN0_224 M.2_RX0_N

224 AV6 MGTHTXP1_224 M2_TX1_P

224 AV5 MGTHTXN1_224 M2_TX1_N

224 AV2 MGTHRXP1_224 M.2_RX1_P

224 AV1 MGTHRXN1_224 M.2_RX1_N

224 AU8 MGTHTXP2_224 M2_TX2_P

224 AU7 MGTHTXN2_224 M2_TX2_N

224 AU4 MGTHRXP2_224 M.2_RX2_P

224 AU3 MGTHRXN2_224 M.2_RX2_N

224 AT6 MGTHTXP3_224 M2_TX3_P

224 AT5 MGTHTXN3_224 M2_TX3_N

224 AT2 MGTHRXP3_224 M.2_RX3_P

224 AT1 MGTHRXN3_224 M.2_RX3_N

65 AJ14 IO_L15N_T2L_N5_AD11N_A03_D19_65 M.2_WAKE#

65 AR13 IO_L7P_T1L_N0_QBC_AD13P_A18_65 M.2_CLKREQ#

65 AE15 IO_T3U_N12_PERSTN0_65 M.2_PERST_#

M.2_REFCLK_P

M.2_REFCLK_N

System Controller

The Neutron board includes a Spartan-7 FPGA that acts as a configuration controller for the Kintex Ultrascale FPGA. The Spartan-7 is used to program the Kintex Ultrascale device via the SelectMAP configuration interface, enabling controlled and flexible configuration of the Kintex Ultrascale FPGA.

This architecture allows the Kintex Ultrascale FPGA to be configured and managed indirectly through the Spartan-7, supporting advanced configuration, boot, and system management use cases.

Contact us for more details about the system controller.

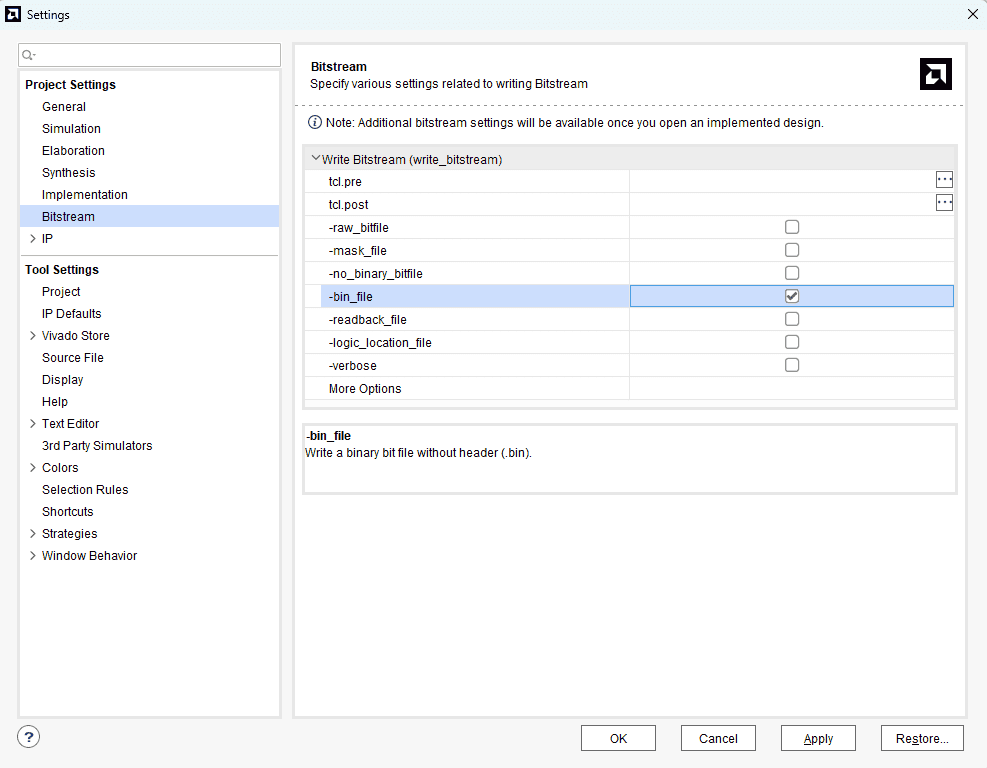

Generating Bitstream for Neutron KU60 FPGA Development Board

The bitstream can be generated for Neutron KU60 FPGA Development Board in Vivado by following the steps below:

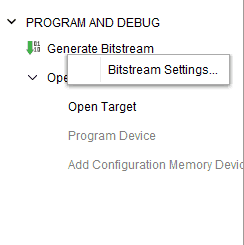

Step 1: It is recommended to generate .bin bitstream file along with .bit bitstream file. Right Click on “Bitstream Settings”.

Step 2: Select “-bin_file*” option in the dialog window and Click “OK”.

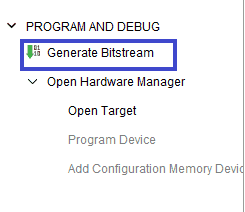

Step 3: Finally click “Generate Bitstream”.

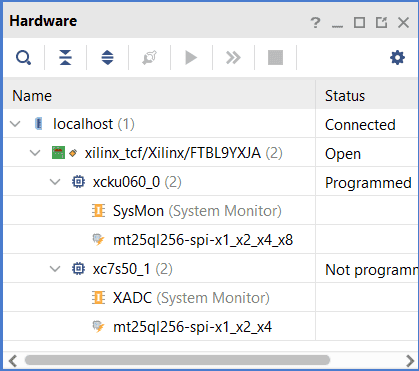

Programming Neutron KU60 FPGA Development Board Using USB-JTAG

1. Ensure that switch SW3 (PGM SEL) is set to USB mode and Connect the USB Type-C cable to the FPGA board.

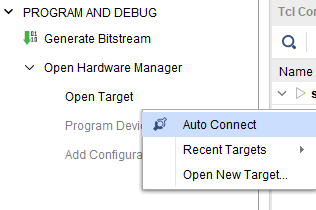

2. Click on “Auto connect” under hardware manager and it will automatically establish the connection.

Programming Neutron KU60 FPGA Development Board Using JTAG

Neutron KU60 FPGA Development Board features an onboard JTAG connector which facilitates easy reprogramming of SRAM and onboard SPI flash through JTAG programmer like “AMD Platform cable USB”. Following steps illustrate how to program FPGA on Neutron KU60 using JTAG.

Step 1: Ensure that switch SW3 is set to JTAG mode.

Step 2: By using JTAG cable, connect AMD platform cable USB to Neutron KU60 and power it up.

Step 3: Open Vivado project and open the target by clicking on the “Open Target” in “Open Hardware Manager” in the “Program and Debug” section of the Flow Navigator window. Select “Auto Connect”.

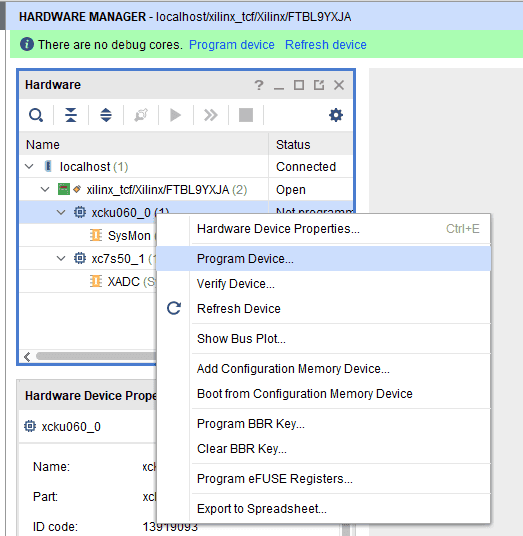

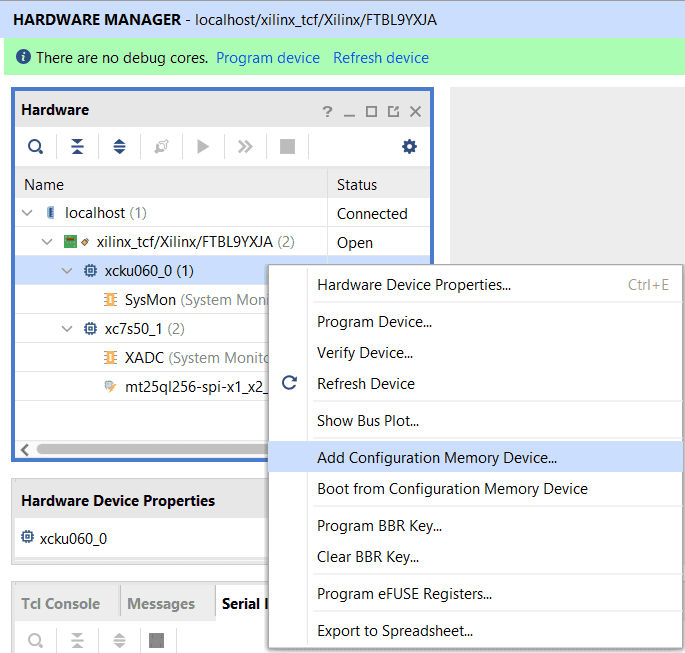

Step 4: If the device is detected successfully, then select “Program Device” after right clicking on the target device “xcku060_0” or “xc7s50_1” as shown below.

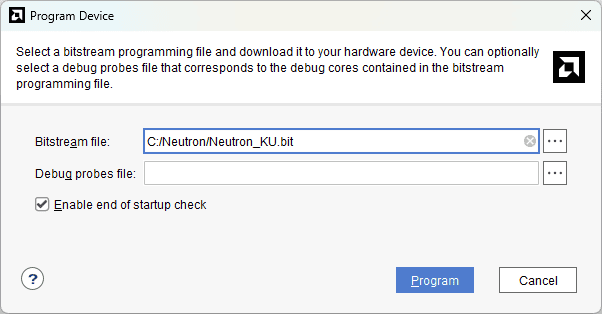

Step 5: In the dialog window which opens up, Vivado automatically chooses correct bitstream file if the design was synthesized, implemented and bitstream generated successfully. If needed, browse to the bitstream which needs to be programmed to FPGA. Finally, click “Program”.

As soon as “Program” is clicked, a orange colored DONE LED (D1) on Neutron KU60 should light up, indicating that programming process is going on. This LED will turn off when the configuration is complete.

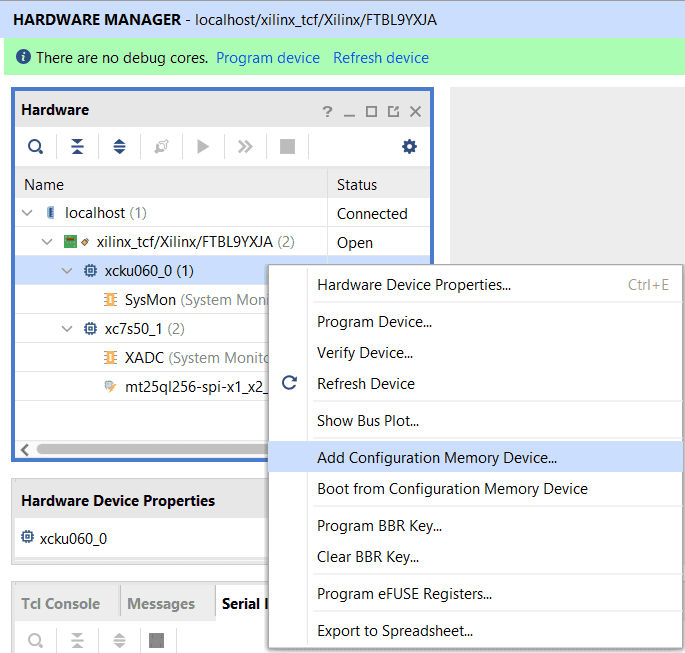

Programming QSPI Flash using Vivado

Single QSPI Programming

A .bin or .mcs file is required for programming Neutron KU60 onboard QSPI flash.

Step 1: Open Vivado project and open the target by clicking on the “Open Target” in “Open Hardware Manager” in the “Program and Debug” section of the Flow Navigator window. Select “Auto Connect”.

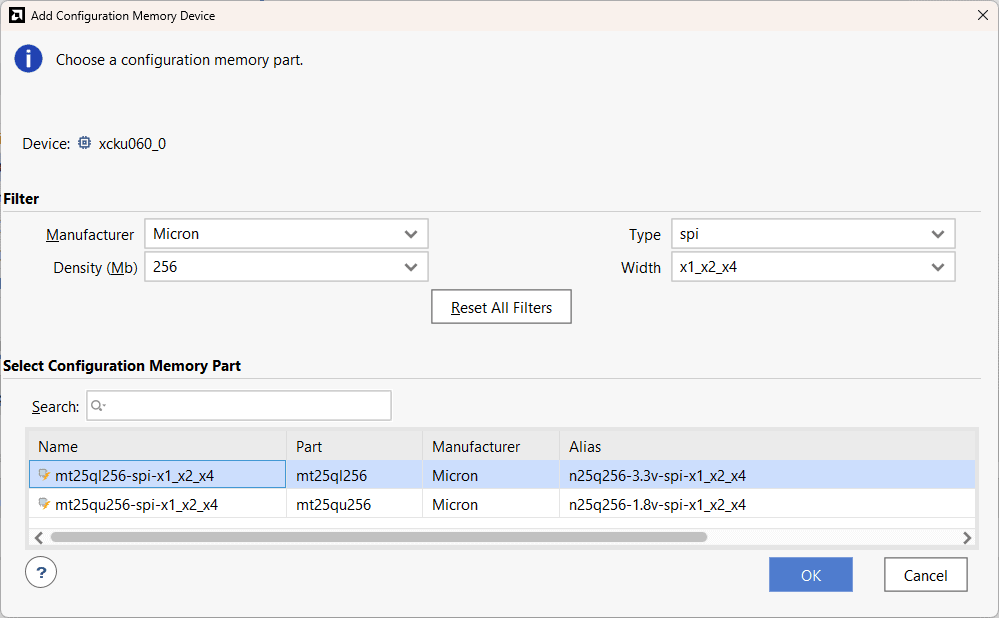

Step 2: If the device is detected successfully, then select “Add Configuration Memory Device” after right clicking on the target device “xcku060_0” or “xc7s50_1” as shown below.

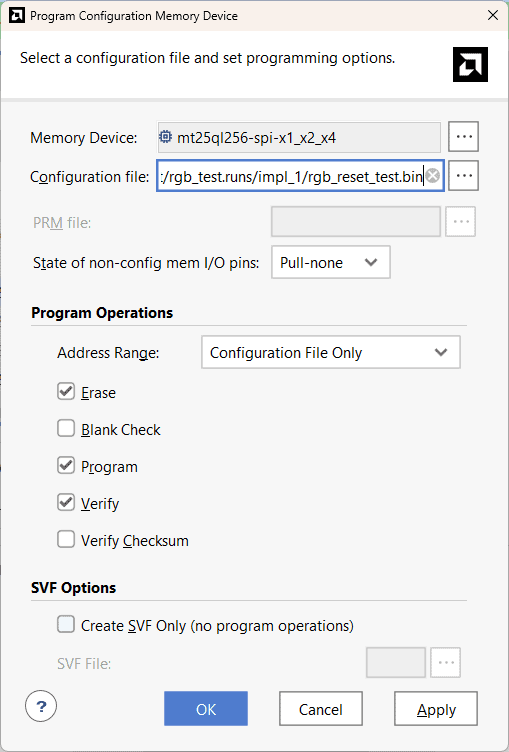

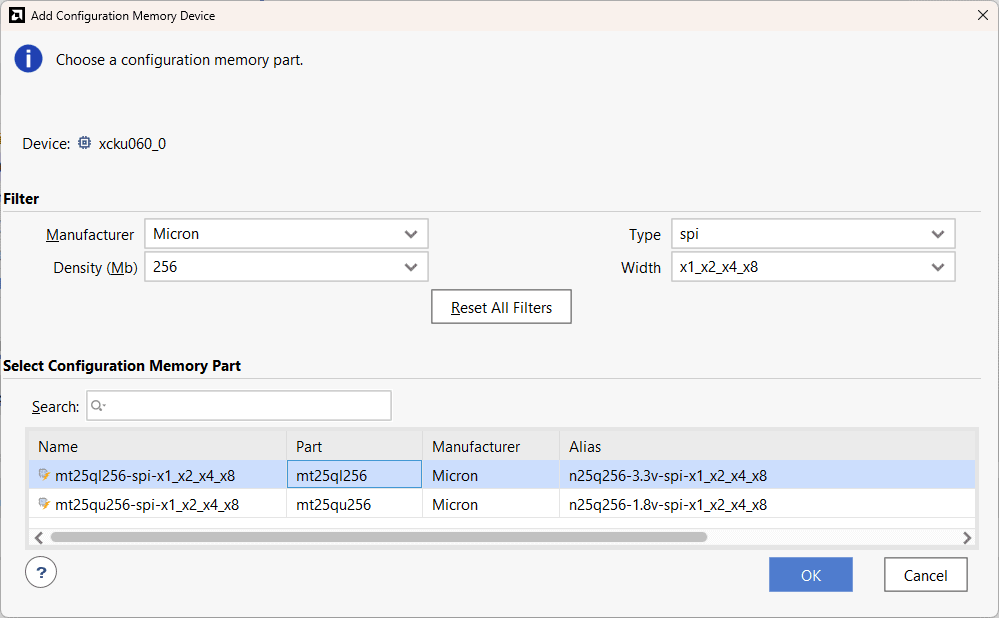

Step 3: Select the memory device “mt25ql256-spi-x1_x2_x4”, then click OK.

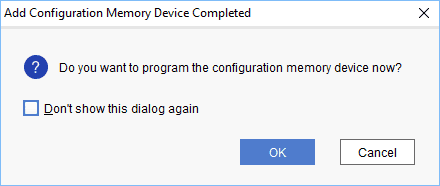

Step 4: After completion of Step 3 the following dialog box will open. Click OK.

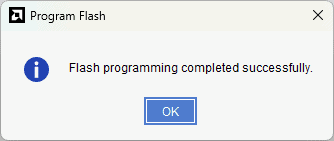

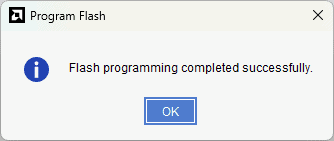

Step 5: Browse to the working .bin file or the .mcs file (whichever applicable) and click OK to program as shown below. If programming is successful, a confirmation message will be displayed.

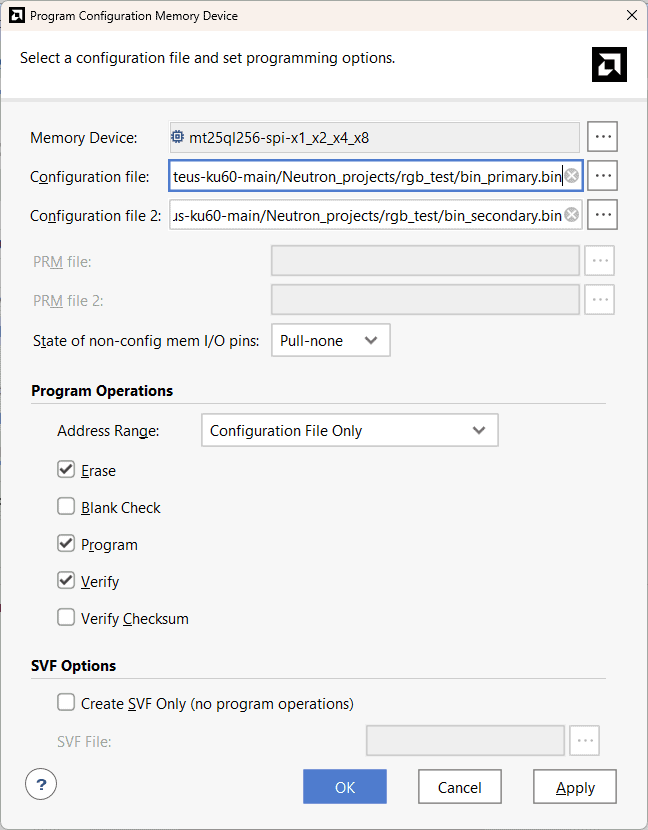

Dual QSPI Programming

Step 1: Open Vivado project and open the target by clicking on the “Open Target” in “Open Hardware Manager” in the “Program and Debug” section of the Flow Navigator window. Select “Auto Connect”.

Step 2: If the device is detected successfully, then select “Add Configuration Memory Device” after right clicking on the target device “xcku060_0” or “xc7s50_1” as shown below.

Step 3: Select the memory device “mt25ql256-spi-x1_x2_x4_x8”, then click OK.

Step 4: After completion of Step 3 the following dialog box will open. Click OK.

Step 5: Browse to the working .bin file or the .mcs file (whichever applicable) and click OK to program as shown below. If programming is successful, a confirmation message will be displayed.

Technical Specifications

Parameter Value Unit

Basic Specifications

Number of GPIOs 320

On-board oscillator frequency (DDR4 CLOCK 300MHz) 300 MHz

On-board oscillator frequency(FABRIC CLOCK 200MHz) 200 MHz

DDR4 Capacity 5 GB

Quad SPI Flash Memory (2x MT25QL256ABA8E2-0AAT) 512 Mb

Power supply voltage (External) 12 V

Programmable Logic Specifications

Internal supply voltage relative to GND –0.500 to 1.100 V

Auxiliary supply voltage relative to GND –0.500 to 2.000 V

HR supply voltage relative to GND –0.500 to 3.400 V

HP supply voltage relative to GND –0.500 to 2.000 V

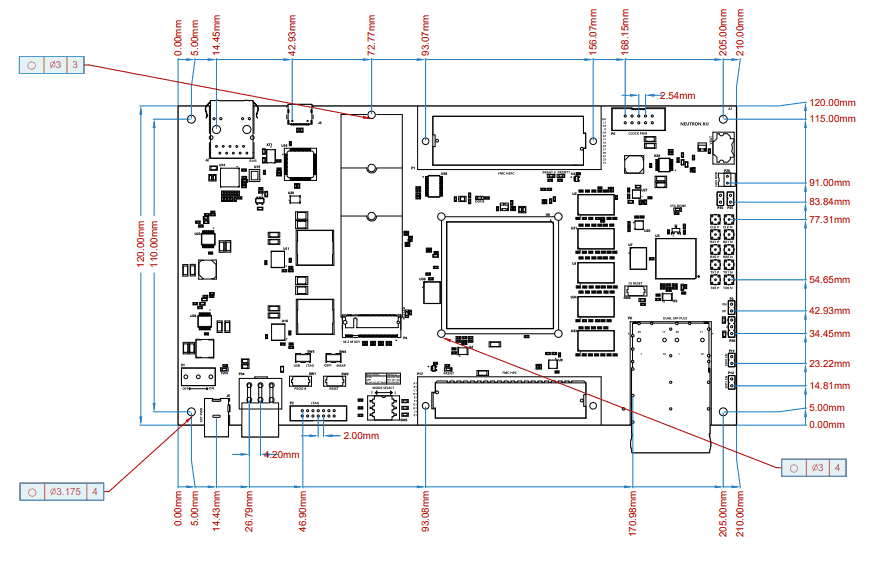

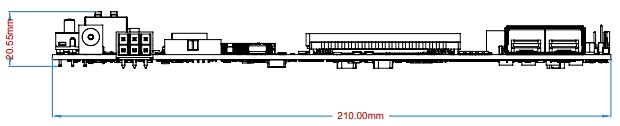

Mechanical Dimensions

Known Issues on Neutron KU60 version A1

- The FMC HPC I²C interface is not functional.

- The FMC+ HSPC I²C interface is not functional.

- The programmable clock (SI5332H-D-GM1) can only be configured using external software. It will be shipped with a default frequency of 100 MHz on all six outputs (customizable based on requirements).

Help Guide Powered by Documentor Neutron KU60 FPGA Development Board

0 views February 5, 2026 megha-m 0